Other Parts Discussed in Thread: HALCOGEN, DP83640

Tool/software:

My goal is to link a library built with ARM FuSa tools into an application built with TI ARM compiler tools.

Using TI ARM tools ti-cfg-arm_20_2_7.LTS, I'm attempting -- and failing -- an ordinary link using of threadx library (built using ARM FuSa tools 6.16.2) and some TI HalCoGen code and C/C++ application code. Both builds work independently. The TI code runs successfully on the ARM HDK. However when I include the threadx_XDER.a library file built with ARM FuSa tools, the TI linker complains and errors (see below). As a restricted capabilities test, I am using the flag --retain with the TI linker to try to force it to retain one of the object files in the threadx_XDER.a library, but get the error:

##################################################

**** Build of configuration Debug for project Config_01_POC ****

"C:\\ti\\ccs1240\\ccs\\utils\\bin\\gmake" -k -j 20 all -O

Building target: "Config_01_POC.out" <*** Successfully completed all compiles ***>

Invoking: Arm Linker

"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/bin/armcl" -mv7R4 --code_state=32 --float_support=VFPv3D16 -me --opt_for_speed=1 --define=XDER_COMPILER_TI_20_2_7_LTS --define=CCS --define=_AEABI_PORTABILITY_LEVEL=1 --define=FPU_PRESENT -g --symdebug:dwarf_version=4 --c11 --diag_wrap=off --display_error_number --issue_remarks --unaligned_access=on --enum_type=packed --wchar_t=16 --common=on --asm_define=__TI_EABI_ASSEMBLER --check_misra="2,-2.2,3,4,6.1,6.2,6.4,6.5,7.1,8,-8.7,-8.12,9,10,-10.1,-10.3,-10.5,-10.6,11,-11.3,-11.4,-11.5,12,-12.1,-12.4,-12.6,-12.7,13,14,15,16,-16.3,-16.7,17,-17.4,18,-18.4,19,-19.4,-19.7,-19.10,-19.12,-19.13,20,-20.1,-20.2,-20.9,-20.11" --misra_advisory=remark --misra_required=error -z -m"Config_01_POC.map" --heap_size=0x1000 --stack_size=0x1000 -i"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/lib" -i"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/include" --reread_libs --disable_auto_rts --diag_remark=1401 --diag_remark=179 --diag_remark=552 --diag_suppress=552 --diag_suppress=179 --diag_wrap=off --display_error_number --issue_remarks --verbose_diagnostics --warn_sections --generate_dead_funcs_list=dead_func_XDER.txt --xml_link_info="Config_01_POC_linkInfo.xml" --retain=threadx_XDER.a<tx_byte_allocate.o> --fill_value=0xfacedeed --rom_model --compress_dwarf=off -o "Config_01_POC.out" "./Config_01_POC_HAL/source/adc.obj" "./Config_01_POC_HAL/source/can.obj" "./Config_01_POC_HAL/source/crc.obj" "./Config_01_POC_HAL/source/dabort.obj" "./Config_01_POC_HAL/source/dcc.obj" "./Config_01_POC_HAL/source/dmm.obj" "./Config_01_POC_HAL/source/emac.obj" "./Config_01_POC_HAL/source/emif.obj" "./Config_01_POC_HAL/source/errata_SSWF021_45.obj" "./Config_01_POC_HAL/source/esm.obj" "./Config_01_POC_HAL/source/gio.obj" "./Config_01_POC_HAL/source/het.obj" "./Config_01_POC_HAL/source/i2c.obj" "./Config_01_POC_HAL/source/lin.obj" "./Config_01_POC_HAL/source/mdio.obj" "./Config_01_POC_HAL/source/mibspi.obj" "./Config_01_POC_HAL/source/notification.obj" "./Config_01_POC_HAL/source/phy_dp83640.obj" "./Config_01_POC_HAL/source/pinmux.obj" "./Config_01_POC_HAL/source/pom.obj" "./Config_01_POC_HAL/source/rti.obj" "./Config_01_POC_HAL/source/rtp.obj" "./Config_01_POC_HAL/source/sci.obj" "./Config_01_POC_HAL/source/spi.obj" "./Config_01_POC_HAL/source/sys_core.obj" "./Config_01_POC_HAL/source/sys_dma.obj" "./Config_01_POC_HAL/source/sys_intvecs.obj" "./Config_01_POC_HAL/source/sys_main.obj" "./Config_01_POC_HAL/source/sys_mpu.obj" "./Config_01_POC_HAL/source/sys_pcr.obj" "./Config_01_POC_HAL/source/sys_phantom.obj" "./Config_01_POC_HAL/source/sys_pmm.obj" "./Config_01_POC_HAL/source/sys_pmu.obj" "./Config_01_POC_HAL/source/sys_selftest.obj" "./Config_01_POC_HAL/source/sys_startup.obj" "./Config_01_POC_HAL/source/sys_vim.obj" "./Config_01_POC_HAL/source/system.obj" "./HET_IslandDER_01/HET_IslandDER_01.obj" "./XDER_code/source_XDER/adc_XDER.obj" "./XDER_code/source_XDER/ems.obj" "./XDER_code/source_XDER/gio_int_handler.obj" "./XDER_code/source_XDER/helpers_xder.obj" "./XDER_code/source_XDER/het_XDER.obj" "./XDER_code/source_XDER/rti_int_handler.obj" "./XDER_code/source_XDER_threadx_demo/threadx_demo.obj" "../Config_01_POC_HAL/source/sys_link.cmd" -l"C:/Users/Kip_Leitner/workspace_v12/Config_01_POC/Debug/rtsv7R4_A_le_v3D16_eabi_debug.lib" -l"C:/ti/Hercules/Cortex-R4 CMSIS DSP Library/1.0.0/Lib/ti_math_Cortex_R4_lspf.lib" -l"C:/Users/Kip_Leitner/Development Studio Workspace/threadx_XDER/Debug/threadx_XDER.a"

makefile:187: recipe for target 'Config_01_POC.out' failed

gmake[1]: *** [Config_01_POC.out] Error 1

makefile:183: recipe for target 'all' failed

gmake: *** [all] Error 2

**** Build Finished ****

Here's the makefile contents:

# All Target

all: $(OBJS) $(CMD_SRCS) $(GEN_CMDS)

<line 183>@$(MAKE) --no-print-directory -Onone "Config_01_POC.out"

# Tool invocations

Config_01_POC.out: $(OBJS) $(CMD_SRCS) $(GEN_CMDS)

<line 187>@echo 'Building target: "$@"'

@echo 'Invoking: Arm Linker'

"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/bin/armcl" -mv7R4 --code_state=32 --float_support=VFPv3D16 -me --opt_for_speed=1 --define=XDER_COMPILER_TI_20_2_7_LTS --define=CCS --define=_AEABI_PORTABILITY_LEVEL=1 --define=FPU_PRESENT -g --symdebug:dwarf_version=4 --c11 --diag_wrap=off --display_error_number --issue_remarks --unaligned_access=on --enum_type=packed --wchar_t=16 --common=on --asm_define=__TI_EABI_ASSEMBLER --check_misra="2,-2.2,3,4,6.1,6.2,6.4,6.5,7.1,8,-8.7,-8.12,9,10,-10.1,-10.3,-10.5,-10.6,11,-11.3,-11.4,-11.5,12,-12.1,-12.4,-12.6,-12.7,13,14,15,16,-16.3,-16.7,17,-17.4,18,-18.4,19,-19.4,-19.7,-19.10,-19.12,-19.13,20,-20.1,-20.2,-20.9,-20.11" --misra_advisory=remark --misra_required=error -z -m"Config_01_POC.map" --heap_size=0x1000 --stack_size=0x1000 -i"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/lib" -i"C:/ti/ccs1240/ccs/tools/compiler/ti-cgt-arm_20.2.7.LTS/include" --reread_libs --disable_auto_rts --diag_remark=1401 --diag_remark=179 --diag_remark=552 --diag_suppress=552 --diag_suppress=179 --diag_wrap=off --display_error_number --issue_remarks --verbose_diagnostics --warn_sections --generate_dead_funcs_list=dead_func_XDER.txt --xml_link_info="Config_01_POC_linkInfo.xml" --retain=threadx_XDER.a<tx_byte_allocate.o> --fill_value=0xfacedeed --rom_model --compress_dwarf=off -o "Config_01_POC.out" $(ORDERED_OBJS)

@echo 'Finished building target: "$@"'

@echo ' '

###########################################

To be absolutely clear, the build of threadx under ARM FuSa works fine. The build of HALCoGen code + my Application code in C and C++ goes fine -- and executes fine. But when I try to link the threadx library into my 20.2.7_LTS build, the build fails. All that gets added is this line:

-l"C:/Users/Kip_Leitner/Development Studio Workspace/threadx_XDER/Debug/threadx_XDER.a

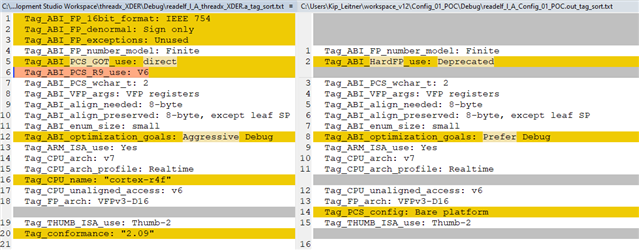

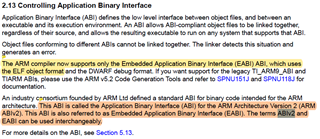

Also, to compare ABI tags, using WSL, I used Linux readelf to dump the ELF information on (a) the threadx_XDER.a library and (b) the final *.out file built with TI tools WITHOUT trying to link the library. Here are the tag differences (left on is ARM FuSa compiler, right is TI 20.2.7_LTS). don't know how to make all the Tags the same, but it seems like both compilers are configured to produce compatible binary outputs.

I'm not sure what might be wrong. Can you help? I've been working on this for three days now.