Other Parts Discussed in Thread: TM4C1294NCPDT

Tool/software:

Hi experts,

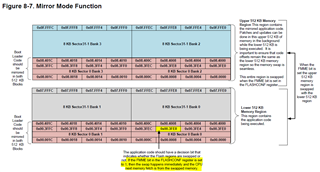

My customer wants to configure flash mirror mode using TM4C1294KCPDT.

some E2E link say that TM4C1294KCPDT does not work in mirror mode.

Please let me know the exact and detailed mirror mode switching sequence including the example source.

thanks

regards