Tool/software:

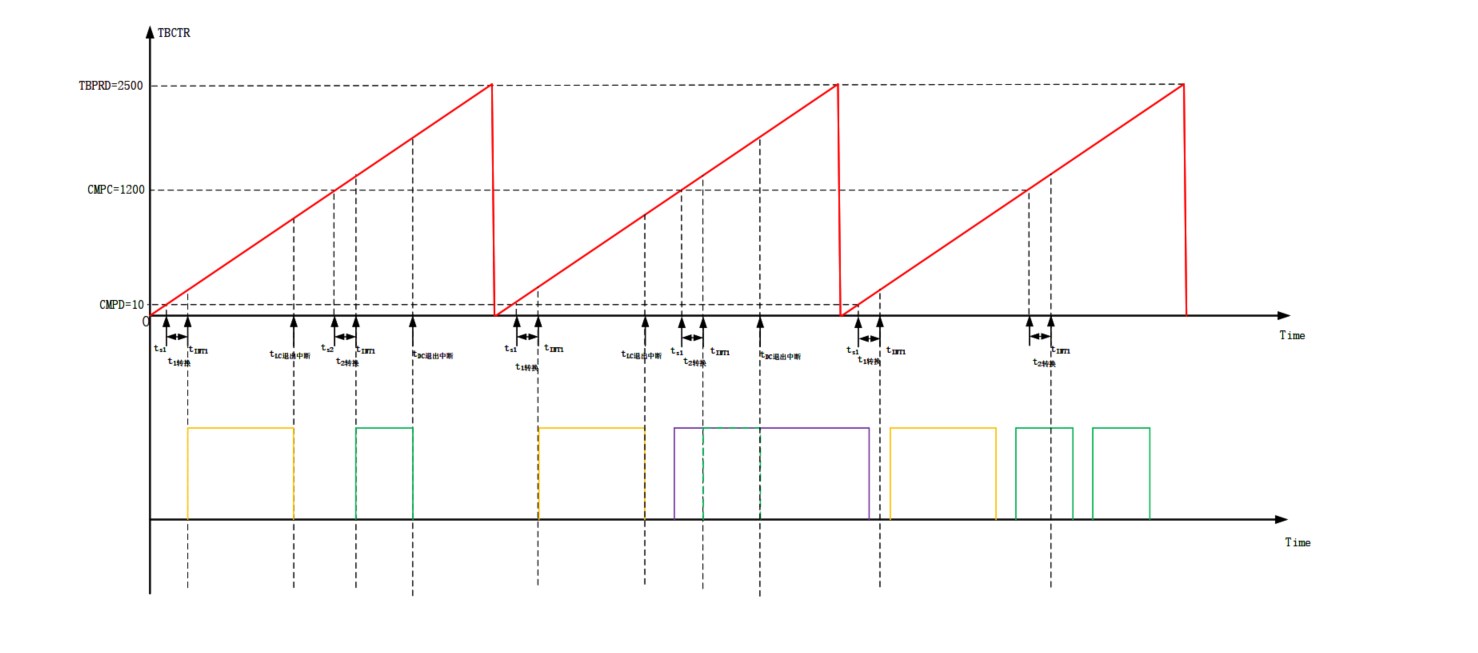

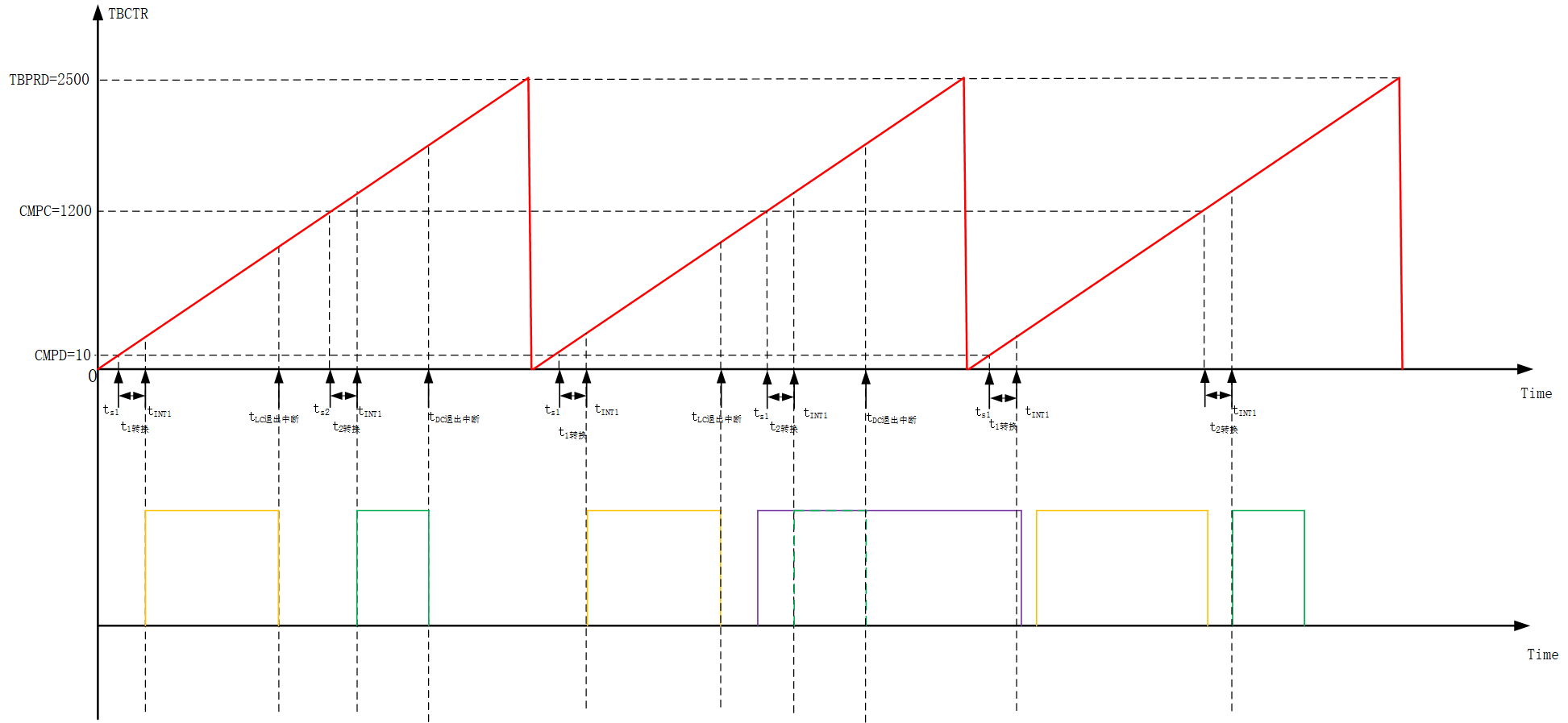

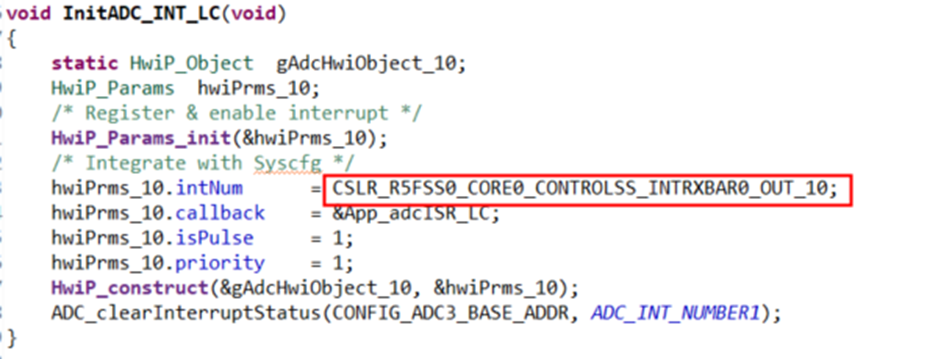

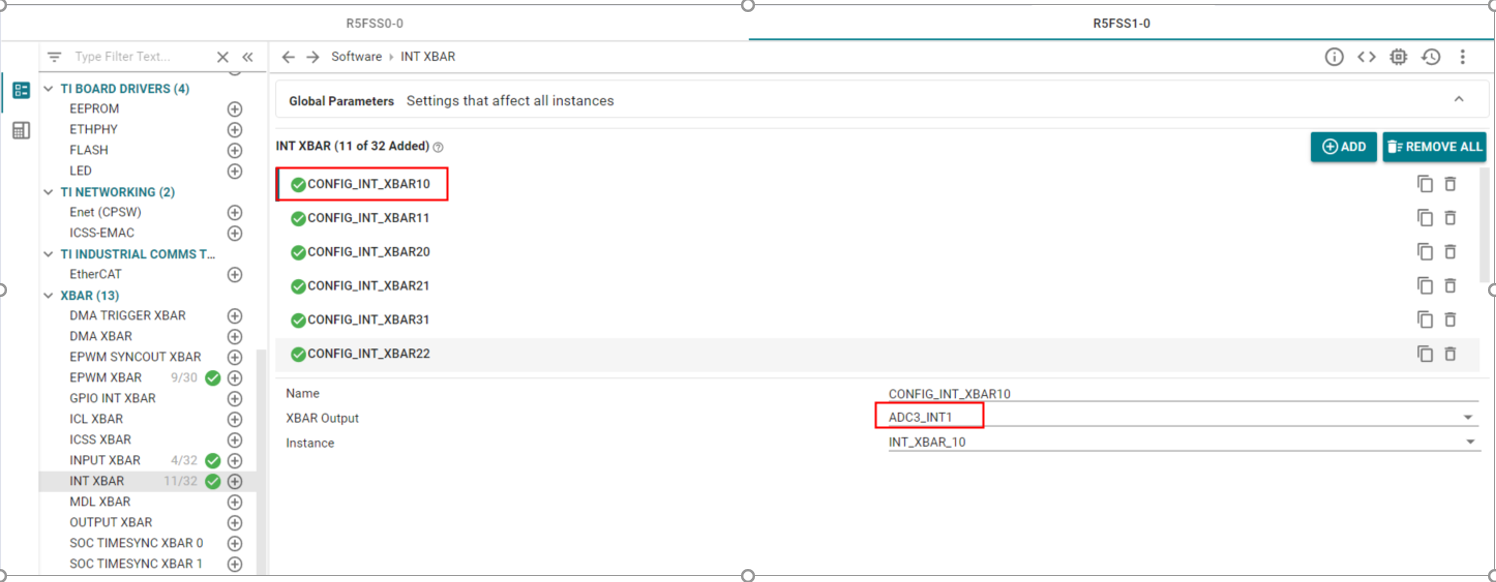

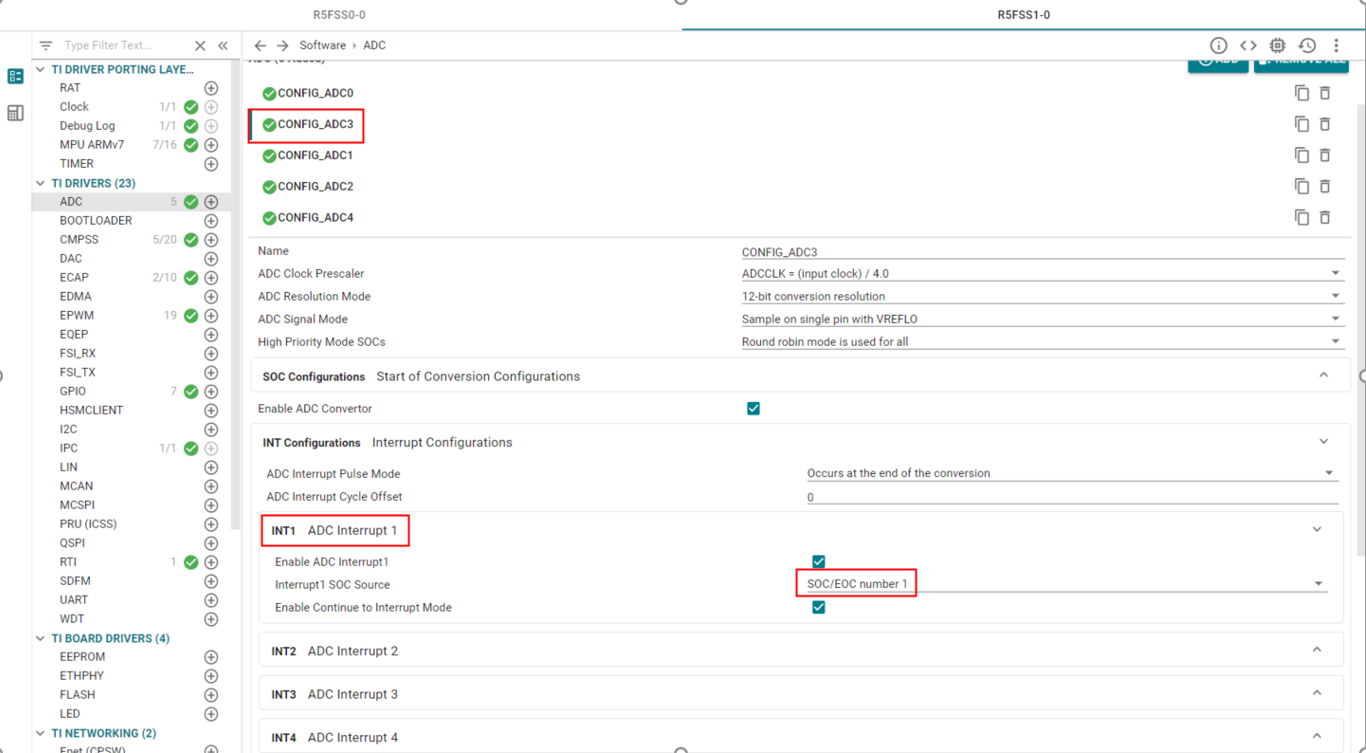

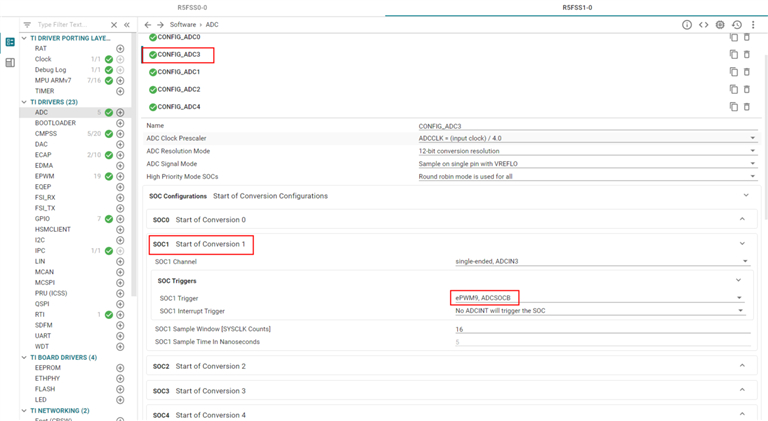

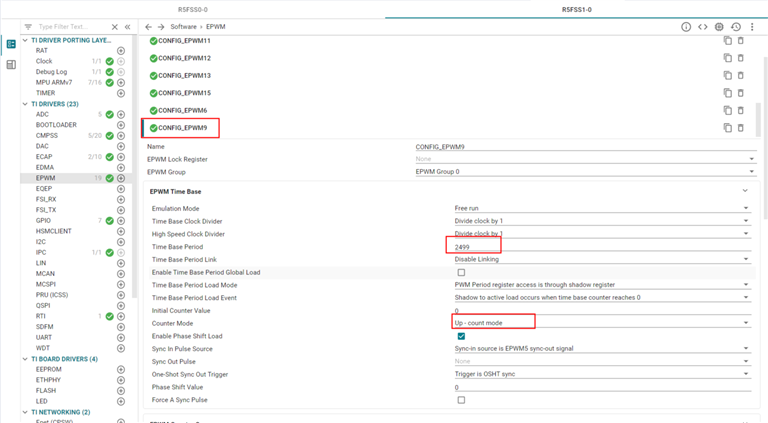

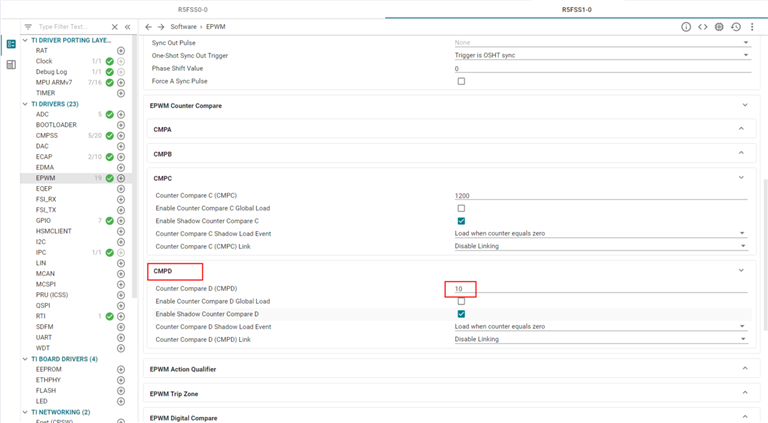

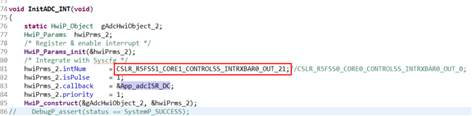

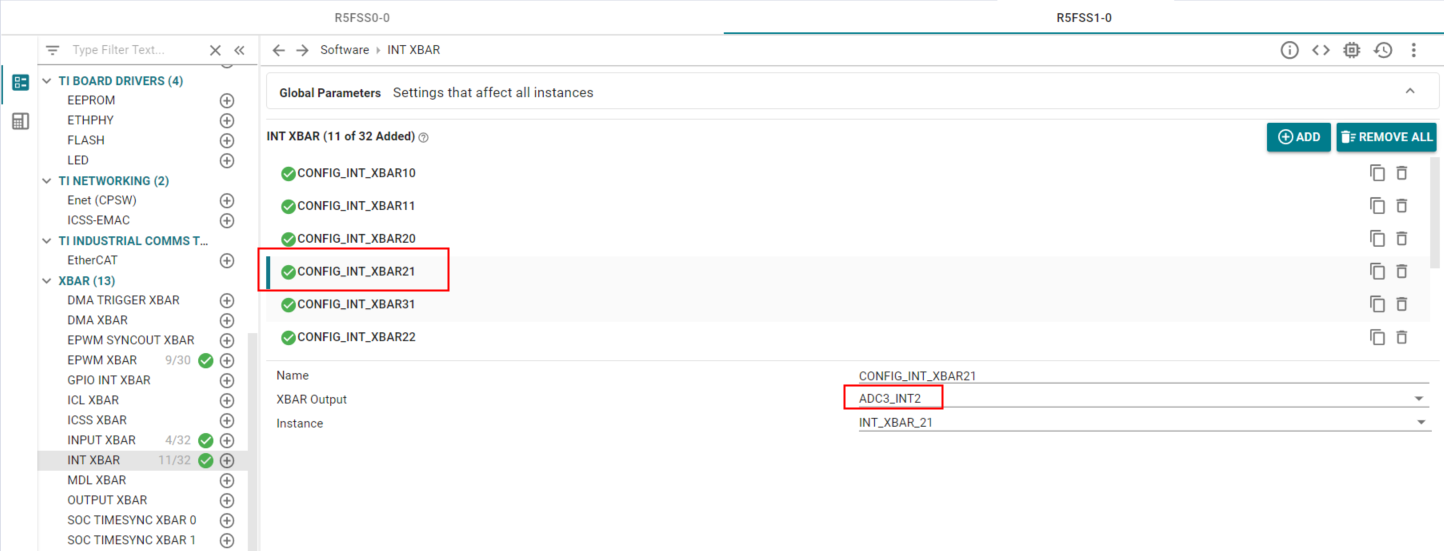

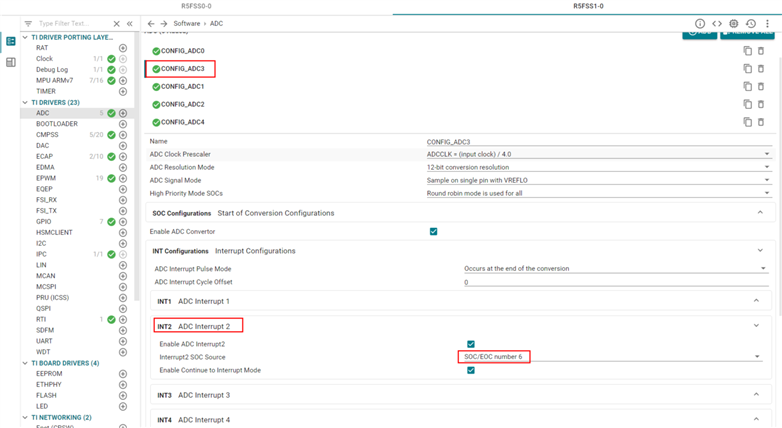

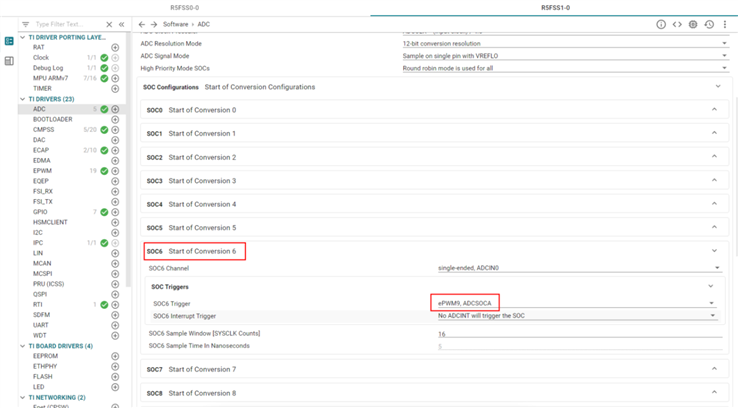

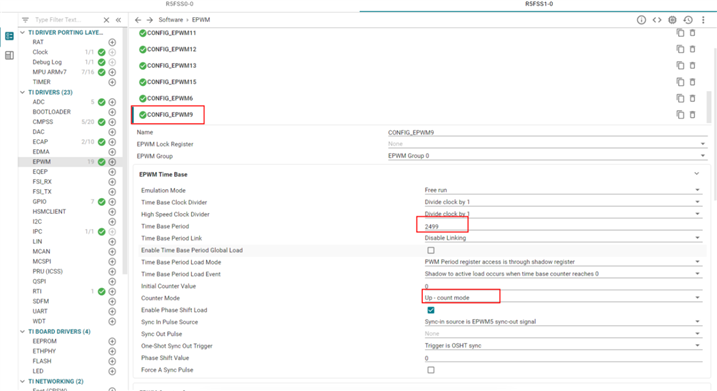

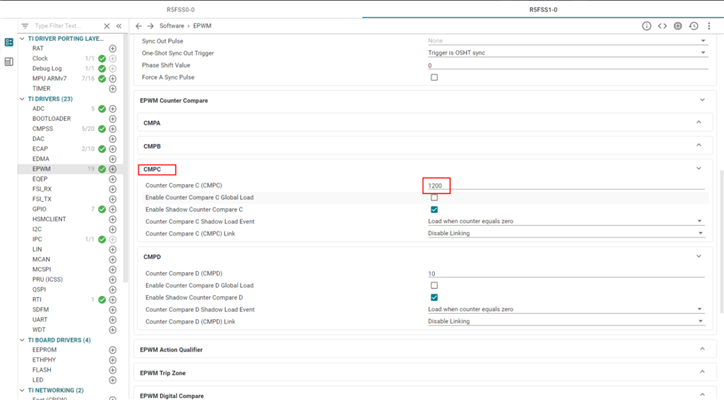

As shown in the figure, the frequency of the carrier is 80k, corresponding to the PRD of 2500, yellow is the interrupt running time of ADCint1 (LC), green is the interrupt running time of ADCint2 (DC), and purple is the interrupt running time of EPWM31 (timer). When CMPD=10, a SOCA pulse event is triggered. At this time, SOC1 of ADC3 channel starts to convert. After time t1 conversion, EOC1 signal is generated to trigger ADCint1 interrupt. When CMPC=1200, a SOCB pulse event is triggered, at this time the SOC3 of the ADC3 channel begins to convert, from SOC3, SOC4, SOC5 to SOC6, SOC6 after time t2 conversion, generating EOC6 signal to trigger the ADCint2 interrupt.

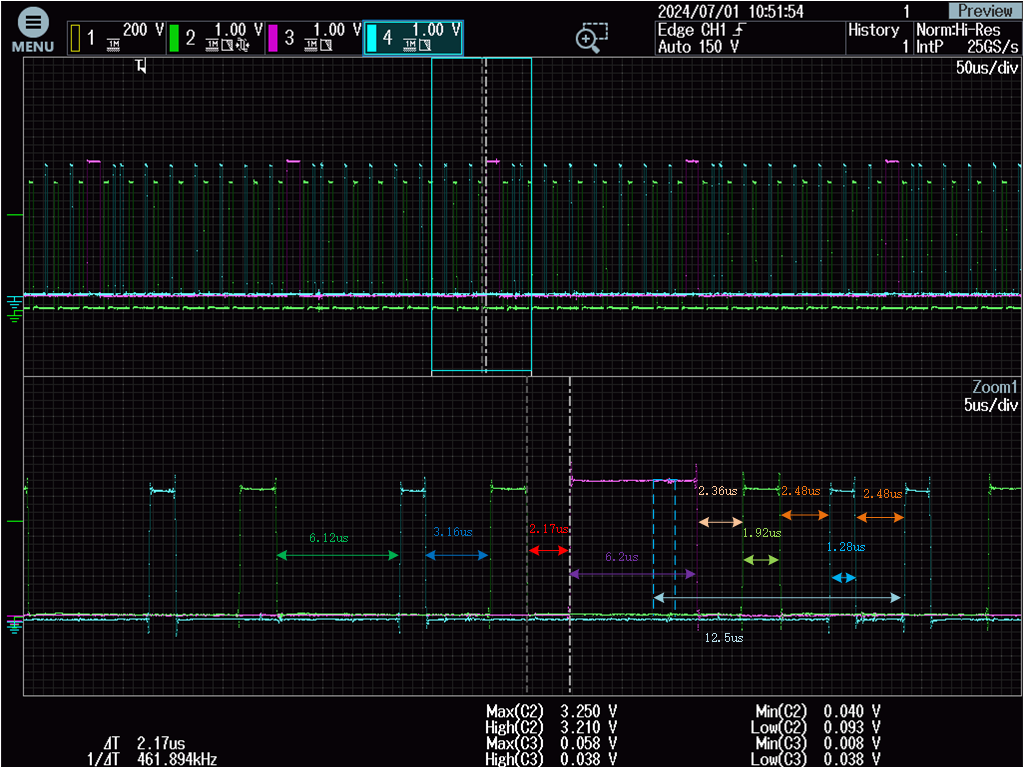

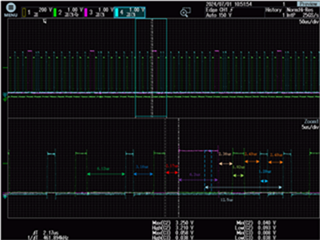

Symptom 1: ADCint2 interrupt is preempted once by EPWM31 interrupt, and ADCint1 interrupt is preempted again

Question 1: As shown in the figure above, why was the ADCint2 (DC) interrupt preempted twice?

Guess why: It may be because the EPWM31 (timer) interrupt precedes the ADCint2 (DC) interrupt, so the ADCint2 (DC) interrupt is delayed by one cycle, and because when the EPWM31 (timer) interrupt ends, EOC1 signal is generated within 2.4us of the interrupt to trigger the ADCint1 (LC) interrupt. Because the response priority of an ADCint1 (LC) interrupt is higher than that of an ADCint2 (DC) interrupt, the ADCint1 (LC) interrupt that runs first results in two consecutive ADCint2 (DC) interrupts.

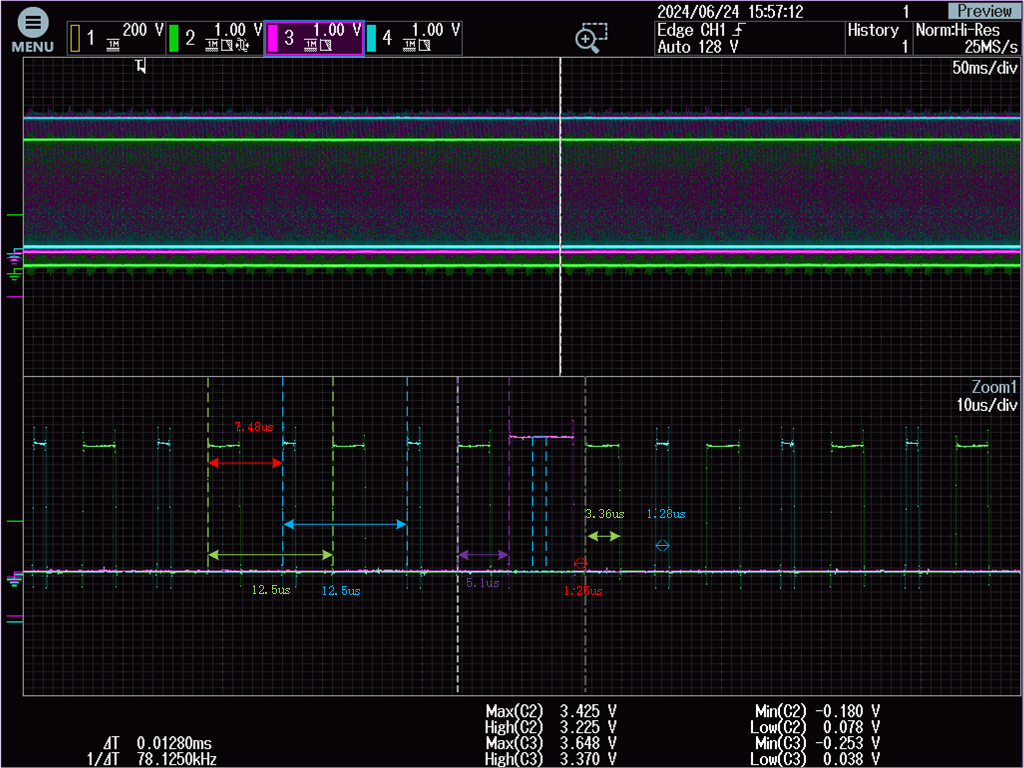

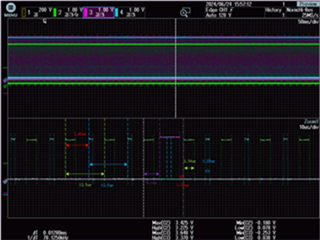

Symptom 1: After the ADCint2 interrupt is preempted by EPWM31 interrupt, the ADCint2 interrupt is preempted by ADCint1 interrupt again, and the ADCINT2 interrupt of the previous period disappears

Question 2: As shown in the figure above, why does an ADCint2 (DC) interrupt disappear after being preempted twice?

Guess why: It may be because the EPWM31 (timer) interrupt precedes the ADCint2 (DC) interrupt, so the ADCint2 (DC) interrupt is delayed by one cycle, and because when the EPWM31 (timer) interrupt ends, EOC1 signal is generated within 2.4us of the interrupt to trigger the ADCint1 (LC) interrupt. Because the response priority of an ADCint1 (LC) interrupt is higher than that of an ADCint2 (DC) interrupt, the ADCint1 (LC) interrupt that runs first causes the ADCint2 (DC) interrupt of the previous cycle to run in this cycle. However, the running time of LC is too long, so that EOC6, the triggering source of ADCint2 (DC) interrupts in the last period, is ignored when SOC6 starts to convert in the current period. As a result, the ADCint2 (DC) interrupts in the last period are ignored, and only the ADCint2 (DC) interrupts in the current period are run.