Tool/software:

Hi,

We are using custom PRU firmware.

Sometimes the CRC32 is not added to the transmitted packets from the PRU.

It seems that it is not in the TX L1 FIFO because the TX FIFO level does not change when TX_CRC_HIGH is set.

So we would like to know the following:

What is the condition to start the TX CRC computation?

Is there a way to reset the TX CRC calculation function?

Our flow is as follws:

1.Check that the RX_SOF bit is 0 in the INTC Raw Status Register 1

2.Change the data path (change MII_RXCFG, MII_TXCFG)

3.TX_RESET

4.Write data

5.Check the TX_FIFO_LEVEL that 8 nibbles or more are free in

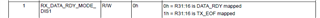

6.cmdR31 [TX_CRC_HIGH + TX_CRC_LOW + TX_EOF]

The data path is "Auto-forward with PRU Snoop" to "32-byte Double Buffer or Ping-Pong Processing".

(TRM 6.4.11.2 MII_G_RT Functional Description)

Observing the operation, it seems that this can occur when the data path settings and the timing of packet reception match.

(After changing the data path, the RX_SOF bit is set in Raw Status Register 1.)

Regards,

Takashi