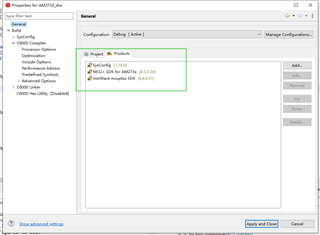

Part Number: AM2732

Tool/software:

hi:

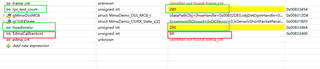

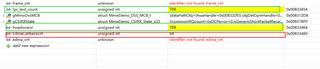

The hwa module triggered the edma channel to transfer data, but it stopped abnormally after only the first frame of data was transferred,

Please help to see what is the reason,thank you!

the part of the hwa and edma codes are shown below:

HWA:

static int32_t rangeProcHWA_ConfigHWA(MmwDemo_DSS_MCB *DSS_MCB)

{

HWA_InterruptConfig paramISRConfig;

int32_t errCode = 0;

int32_t retVal = 0;

uint32_t paramsetIdx = 0;

uint32_t hwParamsetIdx;

HWA_ParamConfig hwaParamCfg[DPU_RANGEPROCHWADDMA_NUM_HWA_PARAM_SETS];

HWA_Handle hwaHandle;

rangeProcHWACompressionCfg *pDPCompParams;

rangeProc_dpParams *pDPParams;

uint8_t index;

uint8_t destChanPing;

uint8_t destChanPong;

hwaHandle = DSS_MCB->dataPathObj.hwaHandle;

pDPParams = &DSS_MCB->StaticCfg_para.dpParams;

pDPCompParams = &DSS_MCB->StaticCfg_para.compressionCfg;

/* In interleave mode, only edmaOutCfgFmt is supported */

retVal = HWA_getDMAChanIndex(hwaHandle, DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_CH, &destChanPing);

if (retVal != 0)

{

goto exit;

}

/* In interleave mode, only edmaOutCfgFmt is supported */

retVal = HWA_getDMAChanIndex(hwaHandle, DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_CH, &destChanPong);

if (retVal != 0)

{

goto exit;

}

memset(hwaParamCfg,0,sizeof(hwaParamCfg));

hwParamsetIdx = DPC_OBJDET_DPU_RANGEPROC_PARAMSET_START_IDX;

for(index = 0; index < DPU_RANGEPROCHWADDMA_NUM_HWA_PARAM_SETS; index++)

{

errCode = HWA_disableParamSetInterrupt(hwaHandle, index + DPC_OBJDET_DPU_RANGEPROC_PARAMSET_START_IDX,

HWA_PARAMDONE_INTERRUPT_TYPE_CPU_INTR1 |HWA_PARAMDONE_INTERRUPT_TYPE_DMA);

if (errCode != 0)

{

goto exit;

}

}

/************************************************/

/* PING 1 INTERFERENCE MITIGATION, FFT PARAMSET */

/************************************************/

{{

hwaParamCfg[paramsetIdx].triggerMode = HWA_TRIG_MODE_HARDWARE;

hwaParamCfg[paramsetIdx].triggerSrc = DPC_OBJDET_HWA_HARDWARE_TRIGGER_SOURCE_M;

hwaParamCfg[paramsetIdx].accelMode = HWA_ACCELMODE_FFT;

/* PREPROC CONFIG */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.dcEstResetMode = HWA_DCEST_INTERFSUM_RESET_MODE_NOUPDATE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.dcSubEnable = HWA_FEATURE_BIT_DISABLE; /* Already done in previous paramset */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.complexMultiply.cmultMode = HWA_COMPLEX_MULTIPLY_MODE_DISABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfStat.resetMode = HWA_DCEST_INTERFSUM_RESET_MODE_NOUPDATE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdEnable = HWA_FEATURE_BIT_DISABLE;//HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdMode = HWA_INTERFTHRESH_MODE_MAGDIFF;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdSelect = HWA_INTERFTHRESH_SELECT_EST_INDIVIDUAL;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.enable = HWA_FEATURE_BIT_DISABLE;//HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.countThreshold = 1;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.pathSelect = HWA_INTERFMITIGATION_PATH_WINDOWZEROOUT;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.leftHystOrder = 3;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.rightHystOrder = 3;

/* ACCELMODE CONFIG (FFT) */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftEn = HWA_FEATURE_BIT_ENABLE;

if(pDPParams->numFFTBins % 3 == 0){

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize = mathUtils_ceilLog2(pDPParams->numFFTBins/3);

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize3xEn = HWA_FEATURE_BIT_ENABLE;

}

else{

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize = mathUtils_ceilLog2(pDPParams->numFFTBins);

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize3xEn = HWA_FEATURE_BIT_DISABLE;

}

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.butterflyScaling = 7; /* 1 << 3 - 1 */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.windowEn = HWA_FEATURE_BIT_DISABLE;//HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.windowStart = DSS_MCB->StaticCfg_para.RangeProcHWA_hwaCfg.hwaWinRamOffset;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.winSymm = HWA_FFT_WINDOW_SYMMETRIC;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.postProcCfg.magLogEn = HWA_FFT_MODE_MAGNITUDE_LOG2_DISABLED;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.postProcCfg.fftOutMode = HWA_FFT_MODE_OUTPUT_DEFAULT;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.complexMultiply.cmultMode = HWA_COMPLEX_MULTIPLY_MODE_DISABLE;

/* SOURCE CONFIG */

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_DCEST_PING_IN]);//DPU_RANGEHWADDMA_MEM_BANK_DCSUB_PING_OUT

hwaParamCfg[paramsetIdx].source.srcAcnt = pDPParams->numAdcSamples - 1; /* this is samples - 1 */

hwaParamCfg[paramsetIdx].source.srcAIdx = (pDPParams->numRxAntennas/2) * pDPParams->sizeOfInputSample;

hwaParamCfg[paramsetIdx].source.srcBcnt = (pDPParams->numRxAntennas/2)-1;

hwaParamCfg[paramsetIdx].source.srcBIdx = pDPParams->sizeOfInputSample;

if(pDPParams->isReal)

{

hwaParamCfg[paramsetIdx].source.srcRealComplex = HWA_SAMPLES_FORMAT_REAL;

}

else

{

hwaParamCfg[paramsetIdx].source.srcRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

}

hwaParamCfg[paramsetIdx].source.srcWidth = HWA_SAMPLES_WIDTH_16BIT;

hwaParamCfg[paramsetIdx].source.srcSign = HWA_SAMPLES_SIGNED;

hwaParamCfg[paramsetIdx].source.srcConjugate = 0;

hwaParamCfg[paramsetIdx].source.srcScale = 8;

/* DEST CONFIG */

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PING_OUT]);

hwaParamCfg[paramsetIdx].dest.dstAcnt = DSS_MCB->StaticCfg_para.valid_numRangeBins-1;//800

hwaParamCfg[paramsetIdx].dest.dstAIdx = pDPParams->numRxAntennas * sizeof(cmplx16ImRe_t);//8

hwaParamCfg[paramsetIdx].dest.dstBIdx = sizeof(cmplx16ImRe_t);

hwaParamCfg[paramsetIdx].dest.dstRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

hwaParamCfg[paramsetIdx].dest.dstWidth = HWA_SAMPLES_WIDTH_16BIT;

hwaParamCfg[paramsetIdx].dest.dstSign = HWA_SAMPLES_SIGNED;

hwaParamCfg[paramsetIdx].dest.dstConjugate = HWA_FEATURE_BIT_DISABLE;

hwaParamCfg[paramsetIdx].dest.dstScale = 0;

hwaParamCfg[paramsetIdx].dest.dstSkipInit = 0;

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

}}

#ifdef CASCADE_EVM

/************************************************/

/* PING 2 INTERFERENCE MITIGATION, FFT PARAMSET */

/************************************************/

{{

paramsetIdx++;

hwParamsetIdx++;

hwaParamCfg[paramsetIdx].triggerMode = HWA_TRIG_MODE_HARDWARE;

hwaParamCfg[paramsetIdx].triggerSrc = DPC_OBJDET_HWA_HARDWARE_TRIGGER_SOURCE_S;

hwaParamCfg[paramsetIdx].accelMode = HWA_ACCELMODE_FFT;

/* PREPROC CONFIG */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.dcEstResetMode = HWA_DCEST_INTERFSUM_RESET_MODE_NOUPDATE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.dcSubEnable = HWA_FEATURE_BIT_DISABLE; /* Already done in previous paramset */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.complexMultiply.cmultMode = HWA_COMPLEX_MULTIPLY_MODE_DISABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfStat.resetMode = HWA_DCEST_INTERFSUM_RESET_MODE_NOUPDATE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdEnable = HWA_FEATURE_BIT_DISABLE;//HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdMode = HWA_INTERFTHRESH_MODE_MAGDIFF;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfLocalize.thresholdSelect = HWA_INTERFTHRESH_SELECT_EST_INDIVIDUAL;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.enable = HWA_FEATURE_BIT_DISABLE;//HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.countThreshold = 1;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.pathSelect = HWA_INTERFMITIGATION_PATH_WINDOWZEROOUT;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.leftHystOrder = 3;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.interfMitigation.rightHystOrder = 3;

/* ACCELMODE CONFIG (FFT) */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftEn = HWA_FEATURE_BIT_ENABLE;

if(pDPParams->numFFTBins % 3 == 0){

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize = mathUtils_ceilLog2(pDPParams->numFFTBins/3);

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize3xEn = HWA_FEATURE_BIT_ENABLE;

}

else{

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize = mathUtils_ceilLog2(pDPParams->numFFTBins);

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.fftSize3xEn = HWA_FEATURE_BIT_DISABLE;

}

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.butterflyScaling = 7; /* 1 << 3 - 1 */

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.windowEn = HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.windowStart = DSS_MCB->StaticCfg_para.RangeProcHWA_hwaCfg.hwaWinRamOffset;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.winSymm = HWA_FFT_WINDOW_SYMMETRIC;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.postProcCfg.magLogEn = HWA_FFT_MODE_MAGNITUDE_LOG2_DISABLED;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.postProcCfg.fftOutMode = HWA_FFT_MODE_OUTPUT_DEFAULT;

hwaParamCfg[paramsetIdx].accelModeArgs.fftMode.preProcCfg.complexMultiply.cmultMode = HWA_COMPLEX_MULTIPLY_MODE_DISABLE;

/* SOURCE CONFIG */

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_DCEST_PING_1_IN]);//DPU_RANGEHWADDMA_MEM_BANK_DCSUB_PING_1_OUT

hwaParamCfg[paramsetIdx].source.srcAcnt = pDPParams->numAdcSamples - 1; /* this is samples - 1 */

hwaParamCfg[paramsetIdx].source.srcAIdx = (pDPParams->numRxAntennas/2) * pDPParams->sizeOfInputSample;

hwaParamCfg[paramsetIdx].source.srcBcnt = (pDPParams->numRxAntennas/2)-1;

hwaParamCfg[paramsetIdx].source.srcBIdx = pDPParams->sizeOfInputSample;

if(pDPParams->isReal)

{

hwaParamCfg[paramsetIdx].source.srcRealComplex = HWA_SAMPLES_FORMAT_REAL;

}

else

{

hwaParamCfg[paramsetIdx].source.srcRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

}

hwaParamCfg[paramsetIdx].source.srcWidth = HWA_SAMPLES_WIDTH_16BIT;

hwaParamCfg[paramsetIdx].source.srcSign = HWA_SAMPLES_SIGNED;

hwaParamCfg[paramsetIdx].source.srcConjugate = 0;

hwaParamCfg[paramsetIdx].source.srcScale = 8;

/* DEST CONFIG */

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PING_1_OUT]) + (pDPParams->numRxAntennas/2) * sizeof(cmplx16ImRe_t);

hwaParamCfg[paramsetIdx].dest.dstAcnt = DSS_MCB->StaticCfg_para.valid_numRangeBins-1;//800

hwaParamCfg[paramsetIdx].dest.dstAIdx = (pDPParams->numRxAntennas) * sizeof(cmplx16ImRe_t);

hwaParamCfg[paramsetIdx].dest.dstBIdx = sizeof(cmplx16ImRe_t);

hwaParamCfg[paramsetIdx].dest.dstRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

hwaParamCfg[paramsetIdx].dest.dstWidth = HWA_SAMPLES_WIDTH_16BIT;

hwaParamCfg[paramsetIdx].dest.dstSign = HWA_SAMPLES_SIGNED;

hwaParamCfg[paramsetIdx].dest.dstConjugate = HWA_FEATURE_BIT_DISABLE;

hwaParamCfg[paramsetIdx].dest.dstScale = 0;

hwaParamCfg[paramsetIdx].dest.dstSkipInit = 0;

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

}}

#endif

#if 1

/*****************************/

/* PING COMPRESSION PARAMSET */

/*****************************/

{{

paramsetIdx++;

hwParamsetIdx++;

hwaParamCfg[paramsetIdx].triggerMode = HWA_TRIG_MODE_IMMEDIATE;

hwaParamCfg[paramsetIdx].accelMode = HWA_ACCELMODE_COMPRESS;

/* ACCELMODE CONFIG */

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.ditherEnable = HWA_FEATURE_BIT_ENABLE; // Enable dither to suppress quantization spurs

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.compressDecompress = HWA_CMP_DCMP_COMPRESS;

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.method = pDPCompParams->compressionMethod;

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.passSelect = HWA_COMPRESS_PATHSELECT_BOTHPASSES;

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.headerEnable = HWA_FEATURE_BIT_ENABLE;

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.scaleFactorBW = 4; //log2(sample bits)

/* SRC CONFIG */

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PING_1_OUT]);

hwaParamCfg[paramsetIdx].source.srcRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

hwaParamCfg[paramsetIdx].source.srcWidth = HWA_SAMPLES_WIDTH_16BIT;

hwaParamCfg[paramsetIdx].source.srcSign = HWA_SAMPLES_SIGNED;

hwaParamCfg[paramsetIdx].source.srcConjugate = HWA_FEATURE_BIT_DISABLE;

hwaParamCfg[paramsetIdx].source.srcScale = 8;

/* DEST CONFIG */

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_COMP_PING_OUT]);

hwaParamCfg[paramsetIdx].dest.dstRealComplex = HWA_SAMPLES_FORMAT_COMPLEX;

hwaParamCfg[paramsetIdx].dest.dstWidth = HWA_SAMPLES_WIDTH_16BIT; /* 16 bit real, 16 bit imag */

hwaParamCfg[paramsetIdx].dest.dstSign = HWA_SAMPLES_UNSIGNED;

hwaParamCfg[paramsetIdx].dest.dstConjugate = HWA_FEATURE_BIT_DISABLE;

hwaParamCfg[paramsetIdx].dest.dstScale = 0;

hwaParamCfg[paramsetIdx].dest.dstSkipInit = 0;

{

/*********************************/

/* PING EGE COMPRESSION PARAMSET */

/*********************************/

hwaParamCfg[paramsetIdx].accelModeArgs.compressMode.EGEKarrayLength = 3; //log2(8)

/* SRC CONFIG */

hwaParamCfg[paramsetIdx].source.srcAcnt = pDPCompParams->inputSamplesPerBlock - 1;//8rx*16rangebin

hwaParamCfg[paramsetIdx].source.srcAIdx = pDPCompParams->bytesPerSample;//4

hwaParamCfg[paramsetIdx].source.srcBcnt = pDPCompParams->numBlocks - 1;//50

hwaParamCfg[paramsetIdx].source.srcBIdx = pDPCompParams->inputBytesPerBlock;//4bytes*8rx*16range

/* DEST CONFIG */

hwaParamCfg[paramsetIdx].dest.dstAcnt = pDPCompParams->outputSamplesPerBlock - 1;

hwaParamCfg[paramsetIdx].dest.dstAIdx = pDPCompParams->bytesPerSample;

hwaParamCfg[paramsetIdx].dest.dstBIdx = pDPCompParams->outputBytesPerBlock;

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

}

/* enable the DMA hookup to this paramset so that data gets copied out */

paramISRConfig.interruptTypeFlag = HWA_PARAMDONE_INTERRUPT_TYPE_DMA;

paramISRConfig.dma.dstChannel = destChanPing;

errCode = HWA_enableParamSetInterrupt(hwaHandle,hwParamsetIdx,¶mISRConfig);

if (errCode != 0)

{

goto exit;

}

}}

#endif

/************************************************/

/* PONG 1 INTERFERENCE MITIGATION, FFT PARAMSET */

/************************************************/

{

paramsetIdx++;

hwParamsetIdx++;

hwaParamCfg[paramsetIdx] = hwaParamCfg[0];

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_DCEST_PONG_IN]);//DPU_RANGEHWADDMA_MEM_BANK_DCSUB_PONG_OUT

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PONG_OUT]);

if(DSS_MCB->StaticCfg_para.dataInputMode != DPU_RangeProcHWA_InputMode_HWA_INTERNAL_MEM)

{

hwaParamCfg[paramsetIdx].triggerSrc = hwParamsetIdx;

}

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

}

#ifdef CASCADE_EVM

/************************************************/

/* PONG 2 INTERFERENCE MITIGATION, FFT PARAMSET */

/************************************************/

{

paramsetIdx++;

hwParamsetIdx++;

hwaParamCfg[paramsetIdx] = hwaParamCfg[1];

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_DCEST_PONG_1_IN]);//DPU_RANGEHWADDMA_MEM_BANK_DCSUB_PONG_OUT

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PONG_1_OUT]) + (pDPParams->numRxAntennas/2) * sizeof(cmplx16ImRe_t);

if(DSS_MCB->StaticCfg_para.dataInputMode != DPU_RangeProcHWA_InputMode_HWA_INTERNAL_MEM)

{

hwaParamCfg[paramsetIdx].triggerSrc = hwParamsetIdx;

}

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

}

#endif

#if 1

/*****************************/

/* PONG COMPRESSION PARAMSET */

/*****************************/

{

paramsetIdx++;

hwParamsetIdx++;

hwaParamCfg[paramsetIdx] = hwaParamCfg[2];

hwaParamCfg[paramsetIdx].source.srcAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_FFT_PONG_1_OUT]);

hwaParamCfg[paramsetIdx].dest.dstAddr = HWADRV_ADDR_TRANSLATE_CPU_TO_HWA(DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_COMP_PONG_1_OUT]);

if(DSS_MCB->StaticCfg_para.dataInputMode != DPU_RangeProcHWA_InputMode_HWA_INTERNAL_MEM)

{

hwaParamCfg[paramsetIdx].triggerSrc = hwParamsetIdx;

}

errCode = HWA_configParamSet(hwaHandle,

hwParamsetIdx,

&hwaParamCfg[paramsetIdx],NULL);

if (errCode != 0)

{

goto exit;

}

/* Enable the DMA hookup to this paramset so that data gets copied out */

paramISRConfig.interruptTypeFlag = HWA_PARAMDONE_INTERRUPT_TYPE_DMA;

paramISRConfig.dma.dstChannel = destChanPong;

errCode = HWA_enableParamSetInterrupt(hwaHandle,

hwParamsetIdx,

¶mISRConfig);

if (errCode != 0)

{

goto exit;

}

}

#endif

exit:

return(errCode);

}

EDMA:

static int32_t rangeProcHWA_ConfigEDMATransposeCompressed(MmwDemo_DSS_MCB *DSS_MCB)

{

DPEDMA_syncABCfg syncABCfg;

int32_t retVal;

int32_t errorCode;

EDMA_Handle handle = DSS_MCB->dataPathObj.edmaHandle[0];

rangeProcHWACompressionCfg *compressionParams = &DSS_MCB->StaticCfg_para.compressionCfg;

rangeProc_dpParams *dpParams = &DSS_MCB->StaticCfg_para.dpParams;

DPEDMA_ChanCfg chanCfg_ping;

DPEDMA_ChanCfg chanCfg_pong;

DPEDMA_ChanCfg chanCfg_Signature;

DPEDMA_ChainingCfg chainingCfg;

uint32_t srcAddress;

uint32_t destAddress;

Edma_IntrObject *intrObj_pong = &DSS_MCB->edmaIntrObjRangeCompOut;

HWA_Handle hwaHandle = DSS_MCB->dataPathObj.hwaHandle;

uint8_t dataOutTrigger[2];

EDMACCPaRAMEntry currPaRAM1,currPaRAM2;

dataOutTrigger[0] = 0;//TRIGGER_PING_HWA_PARAMSET_ID;

dataOutTrigger[1] = 4;//TRIGGER_PONG_HWA_PARAMSET_ID;

srcAddress = DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_COMP_PING_OUT];

destAddress = (uint32_t)DSS_MCB->Mmw_mem_malloc_cfg.radarCube_data;

chainingCfg.chainingChannel = DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_CH;

chainingCfg.isIntermediateChainingEnabled = false;

chainingCfg.isFinalChainingEnabled = false;

DPC_ObjDet_EDMAChannelConfigAssist(handle,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_CH,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_SHADOW,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_SIG_EVENT_QUE,

&chanCfg_Signature);

DPC_ObjDet_EDMAChannelConfigAssist(handle,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_CH,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_SHADOW,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_EVENT_QUE,

&chanCfg_ping);

DPC_ObjDet_EDMAChannelConfigAssist(handle,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_CH,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_SHADOW,

DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_EVENT_QUE,

&chanCfg_pong);

/* Ping */

/* dpedma configuration */

syncABCfg.aCount = compressionParams->outputBytesPerBlock;//8*16*4*0.5

syncABCfg.bCount = compressionParams->numBlocks;//32

syncABCfg.srcBIdx = compressionParams->outputBytesPerBlock;//8*16

syncABCfg.dstBIdx = compressionParams->outputBytesPerBlock*dpParams->numChirpsPerFrame;//8*16*192

syncABCfg.cCount = dpParams->numChirpsPerFrame/2U;//96

syncABCfg.srcCIdx = 0U;

syncABCfg.dstCIdx = compressionParams->outputBytesPerBlock * 2U;//8*16*2

syncABCfg.srcAddress = srcAddress;

syncABCfg.destAddress= destAddress;

retVal = DPEDMA_configSyncAB(handle,

&chanCfg_ping,

&chainingCfg,

&syncABCfg,

true, /* isEventTriggered */

false, /* isIntermediateTransferCompletionEnabled */

false, /* isTransferCompletionEnabled */

NULL,

NULL,

NULL);

if (retVal != SystemP_SUCCESS)

{

goto exit;

}

EDMA_qdmaGetPaRAM(CSL_DSS_TPCC_A_U_BASE, DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PING_CH, &currPaRAM1);

srcAddress = DSS_MCB->StaticCfg_para.hwaMemBankAddr[DPU_RANGEHWADDMA_MEM_BANK_COMP_PONG_OUT];

destAddress = (uint32_t)DSS_MCB->Mmw_mem_malloc_cfg.radarCube_data + compressionParams->outputBytesPerBlock;//

/* Pong */

/* dpedma configuration */

syncABCfg.srcAddress = srcAddress;

syncABCfg.destAddress= destAddress;

retVal = DPEDMA_configSyncAB(handle,

&chanCfg_pong,

&chainingCfg,

&syncABCfg,

true, /* isEventTriggered */

true, /* isIntermediateTransferCompletionEnabled */

true, /* isTransferCompletionEnabled */

rangeProcHWA_EDMA_transferCompletionCallbackFxn,

NULL,

intrObj_pong);

if (retVal != SystemP_SUCCESS)

{

goto exit;

}

// Val = CSL_REG_RD((uint32_t*)(CSL_DSS_TPCC_A_U_BASE + 0x8));

// EDMA_qdmaGetPaRAM(CSL_DSS_TPCC_A_U_BASE, DPC_OBJDET_DPU_RANGEPROC_EDMAOUT_FMT1_PONG_CH, &currPaRAM2);

/**************************************************************************

* HWA hot signature EDMA, chained to the transpose EDMA channels

*************************************************************************/

// errorCode = DPEDMAHWA_configTwoHotSignature(handle,

// &chanCfg_Signature,

// hwaHandle,

// dataOutTrigger[0],

// dataOutTrigger[1],

// false);

// if (errorCode != SystemP_SUCCESS)

// {

// goto exit;

// }