Part Number: MSPM0G3507

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi

May I have advice for my usecase?

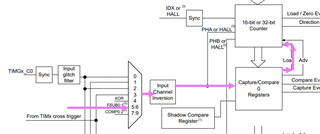

I want to sync each TIMG countor without CPU interrupt.

So I want use generic event route (Subsciber and Publisher port) as sync signal.

And want to set if CC0 recieve subscibe event, generate TIMG countor reset(Load) .

but it is not works.

May I have advice?

I want to do as :

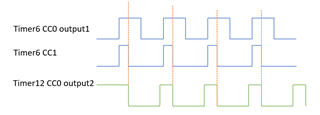

TIMG6 CC1 load event --> event route ID1 --> TIMG12 CC0 input source(IFCTL[0]) -> CC0 Compare event (countor = 1) --> CC0 generate Load event --> TIMG12 countor reset(Load)

I checked TIMG6 generate Load event in CCS debug mode.

(If connect generic route, Load event flag register can not see seted, maybe I think receiver clear flag automatically)

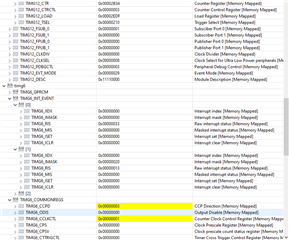

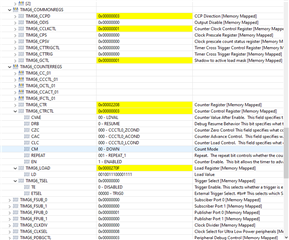

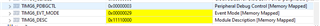

// clock divider

TIMG12->CLKDIV |= GPTIMER_CLKDIV_RATIO_DIV_BY_1; // div = /1, MCLK 80MHz

// clock source

TIMG12->CLKSEL |= GPTIMER_CLKSEL_BUSCLK_SEL_ENABLE; // TIMG6 bus clock is MCLK(80MHz). Please see Datasheet

//clock 2nd prescaler

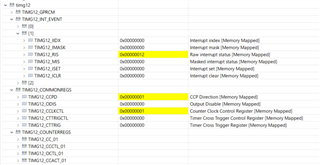

TIMG12->COMMONREGS.CPS |= GPTIMER_CPS_PCNT_MASK & 0x00; // prescale /(8bit+1), dividing 1

// counter register

TIMG12->COUNTERREGS.CTRCTL = 0x00000000; // reset

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_CVAE_ZEROVAL; // when module enabling, countor value set to zero

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_CM_DOWN; // Count down mode

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_REPEAT_REPEAT_1; // Repeat mode

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_DISABLED; // Timer counter disable

// load counter register, using full 16-bit

TIMG12->COUNTERREGS.LOAD |= 0x0000FFFF;

// event

// come from Channel ID1(TIMG6)

//FSUB_0 port

TIMG12->FSUB_0 |= (GPTIMER_FPUB_0_CHANID_MASK & 0x01); // connect channel ID1

// TIMG12->COUNTERREGS.IFCTL_01[0] |= GPTIMER_IFCTL_01_ISEL_FSUB0; //input source = FUSB_0

//setting of crosstriger

TIMG12->COMMONREGS.CTTRIGCTL |= GPTIMER_CTTRIGCTL_EVTCTTRIGSEL_FSUB0; //trigger from FSUB0

TIMG12->COMMONREGS.CTTRIGCTL |= GPTIMER_CTTRIGCTL_EVTCTEN_ENABLE; //input crosstrigger enable

TIMG12->COUNTERREGS.TSEL |= GPTIMER_TSEL_TE_ENABLED; // trigger enable

TIMG12->COUNTERREGS.TSEL |= GPTIMER_TSEL_ETSEL_TRIG_SUB0; // trigger from FSUB0

//setting CC0 imput source

TIMG12->COUNTERREGS.IFCTL_01[0] |= GPTIMER_IFCTL_01_ISEL_TRIG_INPUT; //input source = trigger

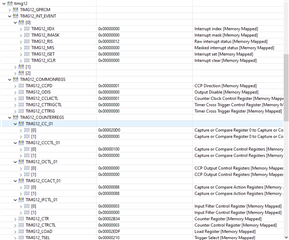

//setting CC0

TIMG12->COUNTERREGS.CC_01[0] |= (GPTIMER_CC_01_CCVAL_MASK & 0x1); // compare value

TIMG12->COUNTERREGS.CCCTL_01[0] |= GPTIMER_CCCTL_01_COC_CAPTURE; // capture mode

TIMG12->COUNTERREGS.CCCTL_01[0] |= GPTIMER_CCCTL_01_CCOND_CC_TRIG_RISE; //capture rising edge

TIMG12->COUNTERREGS.OCTL_01[0] |= GPTIMER_OCTL_01_CCPO_LOAD; // output load event

// Capture or Compare (CCP) setting

TIMG12->COMMONREGS.CCPD |= GPTIMER_CCPD_C0CCP1_OUTPUT; // TIMG12_CCP1 output

TIMG12->COMMONREGS.ODIS &= ~(GPTIMER_ODIS_C0CCP1_MASK); // CCP1 is output, not forced Low

TIMG12->COUNTERREGS.CC_01[1] |= (GPTIMER_CC_01_CCVAL_MASK & 135); // compare value

TIMG12->COUNTERREGS.CCCTL_01[1] |= GPTIMER_CCCTL_01_COC_COMPARE; // Compare mode

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPIV_LOW; // initvalue = low output

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPOINV_INV; // output is inversion

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPO_FUNCVAL; // Output source = Signal generator value

TIMG12->COUNTERREGS.CCACT_01[1] |= GPTIMER_CCACT_01_LACT_CCP_LOW; // Load event = set Low

TIMG12->COUNTERREGS.CCACT_01[1] |= GPTIMER_CCACT_01_CDACT_CCP_HIGH; // Compare event = set high

// enabling clock

TIMG12->COMMONREGS.CCLKCTL |= GPTIMER_CCLKCTL_CLKEN_ENABLED; // clock enabled

//Before main roop

TIMG6->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_ENABLED; // Timer counter enable

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_ENABLED; // Timer counter enable

CC compare value is 0x1, so if there is recieved one event will generate compare event.

If it work as I think, TIMG12CC1output period must be same as TIMG6 PWM.

(Load value is TIMG12>TIMG6, so TIMG6 generate load event(=transmit as TIMG12 load event) before TIMG12 PWM priod. So each priod will be same)

Thanks,

GR