Part Number: TMS570LC4357

Other Parts Discussed in Thread: HALCOGEN

Tool/software:

Hi experts,

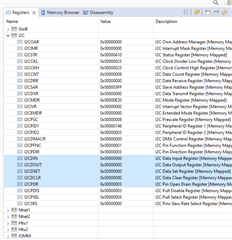

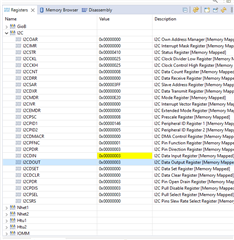

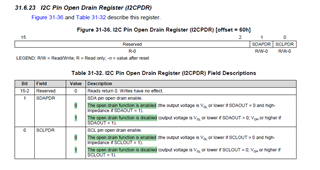

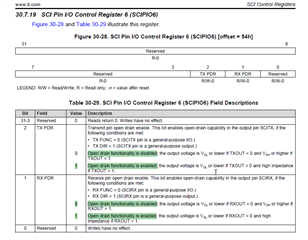

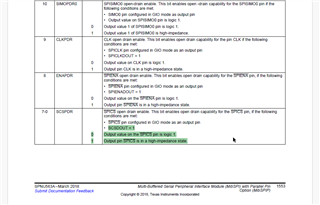

In the description of the I2CPDR register (Table 31-32) in the Technical Reference Manual, the bits are described as follows:

SCLPDR:

0 - Open drain function is enabled

1 - Open drain function is disabled

This differs from the description in other PDR registers (e.g. Table 25-19. GIOPDR). Normally a setting of 0 disables open drain and enables push/pull and a setting of 1 enables open drain.

- Is this an error in the description of the i2CPDR register or is the configuration for this register different?

- Is there no push/pull functionality?

Thanks and best regards,

Max