Part Number: TMS570LS3137

Tool/software:

Hi,

The Hercules TRM states:

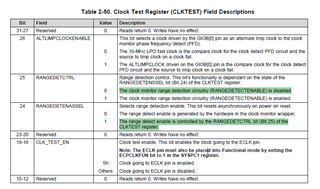

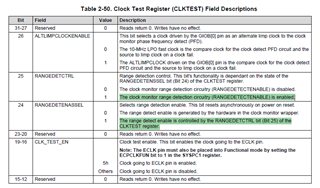

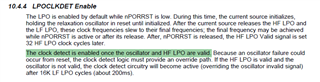

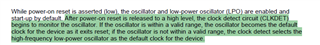

10.4.4 LPOCLKDET Enable The LPO is enabled by default while nPORRST is low. During this time, the current source initializes, holding the relaxation oscillator in reset until initialized. After the current source releases the HF LPO and the LF LPO, these clock frequencies slew to their final frequencies; the final frequency may be achieved while nPORRST is active or after its release. After, nPORRST is released, the HF LPO Valid signal is set 32 HF LPO clock cycles later. The clock detect is enabled once the oscillator and HF LPO are valid. Because an oscillator failure could occur from reset, the clock detect logic must provide an override path. If the HF LPO is valid and the oscillator is not valid, the clock detect circuitry will become active (overriding the oscillator invalid signal) after 16K LF LPO cycles (about 200ms)

However, if I short the OSCIN pin to ground and try to do RST/PORRST/power cycle, the MCU does not seem to start.

May someone provide insight regarding:

- Is there a way to "debug" the validity of the oscillator and the LPO during/right after RST/PORRST?

- Is an ext. oscillator fault event required to trigger the switching to the LPO?

- Is it possible to start (after power-up) and run the Hercules without the external oscillator?

Thanks!