Tool/software:

Dear expert,

Recently, I found that MCAL_AM273x_09.01.00 can cause AM2732 ethernet transmit interrupt (MSS_CPSW_FH_INT) to be abnormal in some cases.

The case is like this: Suspend all interrupts through Os, transmit ethernet messages ten times in a loop, and then resume all interrupts through Os.

By analyzing the logic of the mcal source code, I think the first interrupt should send the first frame,

then in the first transmit intrrrupt continue to call CPDMA to send the remaining ethernet packets,and trigger the ethernet transmit interrupt again.

However, the actual phenomenon is that the transmit interrupt only entered once and did not enter the second time.

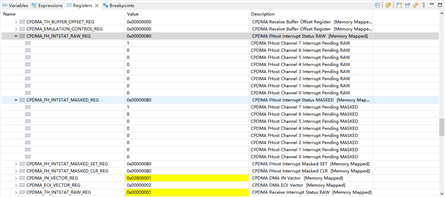

According to the CPDMA register, the interrupt is in a pending state and has not been triggered.

May I ask if this is a known issue? If not, can you provide me with some help based on this issue?

Regards,

Ning Wang