Other Parts Discussed in Thread: MSPM0G1105, MSPM0G1106, MSPM0G1107, MSPM0G1505, MSPM0G1506, MSPM0G1507, MSPM0G3105, MSPM0G3106, MSPM0G3107, MSPM0G3505, MSPM0G3506, MSPM0G3507, MSPM0L1227, MSPM0L1228, MSPM0L2227, MSPM0L2228

Tool/software:

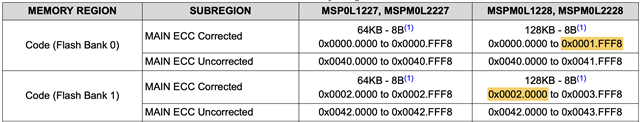

The datasheet for MSPM0L1105 states the following:

CPU access to one of the last 8 bytes of a flash region will cause a hard fault. This occurs because the prefetch logic tries to read one flash word (64 bits) ahead, resulting in a read attempt to an invalid memory location.

Does this refer only to instruction accesses, or does this apply to data accesses too? Do data accesses have prefetch logic that would cause the CPU to read more than what is requested?