Part Number: MCU-PLUS-SDK-AM263X

Tool/software:

I have been having issues debugging multi-core applications since I’ve been using AM263Px. The symptom is that if multiple cores run simultaneously with both cores attached. I am using SBL_NULL (not DEV_BOOT) on AM263Px Control Card Evaluation Module. The symptoms I see is an Abort Exception.

SDK Version:

mcu_plus_sdk_am263px_09_02_00_56

I created a thread here:

… but moved on to other work, never resolving the issue.

I also see related discussions:

I reviewed these, but I do not see a solution in those threads.

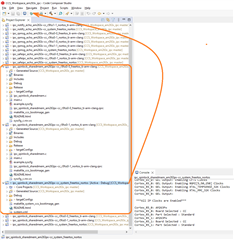

I am using example SDK project:

/ipc_spinlock_sharedmem_am263px-cc_system_freertos_nortos

… to demonstrate here.

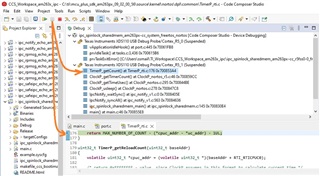

- Select System Project and click “Debug”

- This triggers the following output in the Console:

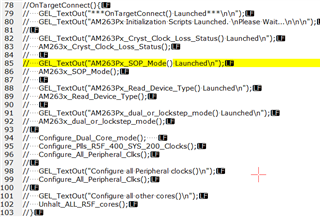

Cortex_R5_0: GEL Output: Gel files loading on R5F0 Complete

Cortex_R5_0: GEL Output: ***OnTargetConnect() Launched***

Cortex_R5_0: GEL Output: AM263Px Initialization Scripts Launched.

Please Wait...

Cortex_R5_0: GEL Output: AM263Px_Cryst_Clock_Loss_Status() Launched

Cortex_R5_0: GEL Output: Crystal Clock present

Cortex_R5_0: GEL Output: AM263Px_SOP_Mode() Launched

Cortex_R5_0: GEL Output: SOP MODE = 0x00000003

Cortex_R5_0: GEL Output:

OSPI - 8S Functional boot mode

Cortex_R5_0: GEL Output: AM263Px_Read_Device_Type() Launched

Cortex_R5_0: GEL Output: EFuse Device Type Value = 0x000000AA

Cortex_R5_0: GEL Output: AM263Px_dual_or_lockstep_mode() Launched

Cortex_R5_0: GEL Output: r5fss0 = 0x00000001

Cortex_R5_0: GEL Output: r5fss1 = 0x00000000

Cortex_R5_0: GEL Output:

R5FSS0 is in Dual core mode

Cortex_R5_0: GEL Output:

R5FSS1 is in Dual core mode

Cortex_R5_0: GEL Output: MSS_CTRL Control Registers Unlocked

Cortex_R5_0: GEL Output: MSS_TOP_RCM Control Registers Unlocked

Cortex_R5_0: GEL Output: MSS_RCM Control Registers Unlocked

Cortex_R5_0: GEL Output: MSS_IOMUX Control Registers Unlocked

Cortex_R5_0: GEL Output: TOP_CTRL Control Registers Unlocked

Cortex_R5_0: GEL Output:

*** R5FSS0 Reset DualCore ***

Cortex_R5_0: GEL Output:

***R5FSS1 Reset DualCore ***

Cortex_R5_0: GEL Output: R5F ROM Eclipse

Cortex_R5_0: GEL Output: R5FSS0_0 Released

Cortex_R5_0: GEL Output: R5FSS0_1 Released

Cortex_R5_0: GEL Output: R5FSS1_0 Released

Cortex_R5_0: GEL Output: R5FSS1_1 Released

Cortex_R5_0: GEL Output: L2 Mem Init Complete

Cortex_R5_0: GEL Output: MailBox Mem Init Complete

Cortex_R5_0: GEL Output: *********** R5FSS0/1 Dual Core mode Configured********

Cortex_R5_0: GEL Output: SYS_CLK DIVBY2

Cortex_R5_0: GEL Output: DPLL_CORE_HSDIV0_CLKOUT0 selected as CLK source for R5FSS & SYS CLKs

Cortex_R5_0: GEL Output:

CLK Programmed R5F=400MHz and SYS_CLK=200MHz

Cortex_R5_0: GEL Output:

*** Enabling Peripheral Clocks ***

Cortex_R5_0: GEL Output: Enabling RTI[0:3] Clocks

Cortex_R5_0: GEL Output: Enabling RTI_WDT[0:3] Clocks

Cortex_R5_0: GEL Output: Enabling UART[0:5]/LIN[0:5] Clocks

Cortex_R5_0: GEL Output: Enabling QSPI Clocks

Cortex_R5_0: GEL Output: Enabling I2C Clocks

Cortex_R5_0: GEL Output: Enabling TRACE Clocks

Cortex_R5_0: GEL Output: Enabling MCAN[0:3] Clocks

Cortex_R5_0: GEL Output: Enabling MMCSD Clocks

Cortex_R5_0: GEL Output: Enabling MCSPI[0:4] Clocks

Cortex_R5_0: GEL Output: Enabling CONTROLSS Clocks

Cortex_R5_0: GEL Output: Enabling CPTS Clocks

Cortex_R5_0: GEL Output: Enabling RGMI[5,50,250] Clocks

Cortex_R5_0: GEL Output: Enabling XTAL_TEMPSENSE_32K Clocks

Cortex_R5_0: GEL Output: Enabling XTAL_MMC_32K Clocks

Cortex_R5_0: GEL Output:

***All IP Clocks are Enabled***

Cortex_R5_0: AM263Px

Cortex_R5_0: Board Selected : CC

Cortex_R5_0: Part Selected : Standard

Cortex_R5_1: AM263Px

Cortex_R5_1: Board Selected : CC

Cortex_R5_1: Part Selected : Standard

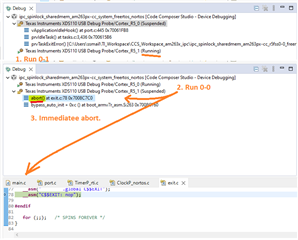

3)

Eventually both cores are halted at main.

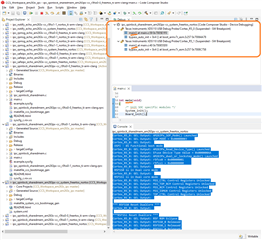

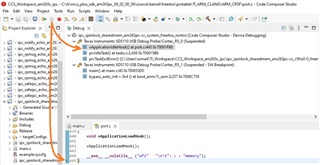

4)

I can run core r5fss0-0, and halt it while core r5fss0-1 is halted.

5)

I can run core r5fss0-1, and halt it while core r5fss0-0 is halted.

6)

However, when I run If I try to run simultaneously by starting core r5fss0-1, and then starting r5fss0-0, an abort occurs immediately on r5fss0-1.

Please advise.