Tool/software:

There is a method to flush the fifo of UART and MCSPI: read all of the data until the fifo is empty.

Is there another way to flush or reset the fifo of UART and MCSPI? Is there a register which can implement the function?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

There is a method to flush the fifo of UART and MCSPI: read all of the data until the fifo is empty.

Is there another way to flush or reset the fifo of UART and MCSPI? Is there a register which can implement the function?

Hi Xiaoxue Zhang,

UART:

If you are using UART LLD, you can call the API: UART_lld_flushTxFifo()

From registers point of view:

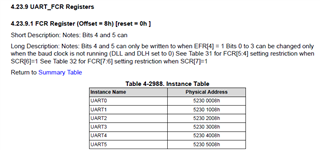

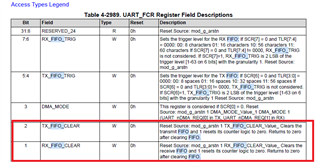

The UART_FCR register has the 2nd Bit for clearing the TX_FIFO and the 1st bit for clearing the RX_FIFO

McSPI:

I'm not the expert on McSPI, I will wait for the appropriate expert to answer the mechanisms to reset/clear the McSPI FIFO

Regards,

Shaunak

Hi Xiaoxue,

You don't have to clear the FIFO or data register before next transmission. You can use the interrupt status (RX_FULL and TX_EMPTY in IRQSTATUS register) and TX or RX count. The end of transfer depends on the transfer mode.

Please refer to 13.1.3.5 MCSPI Programming Guide of device TRM (Page 1036)

AM263x Sitara Microcontroller Technical Reference Manual (Rev. F) (ti.com)