Other Parts Discussed in Thread: TMS570LC4357,

Tool/software:

Good afternoon,

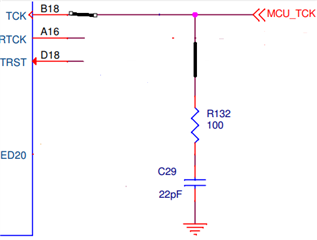

I am currently working on a custom board featuring the TMS570LC4357 microcontroller and have encountered an issue when attempting to connect it to Code Composer Studio (CCS). Specifically, I receive a "cable break" error.

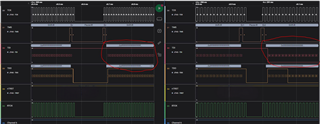

I have verified that my custom board uses the same FTDI chip as the evaluation board. However, despite this similarity, my board fails to connect properly. I have analyzed the signal data from both the evaluation board and my custom board using Saleae Logic 2 software. The results indicate a failure during the connection process on my custom board.

Could there be any specific checks or configurations in CCS that might not be compatible with my custom board? I have attached the signal readings for your reference.

I appreciate any guidance or insights you can provide.

Best regards,

Miguel Catana