Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

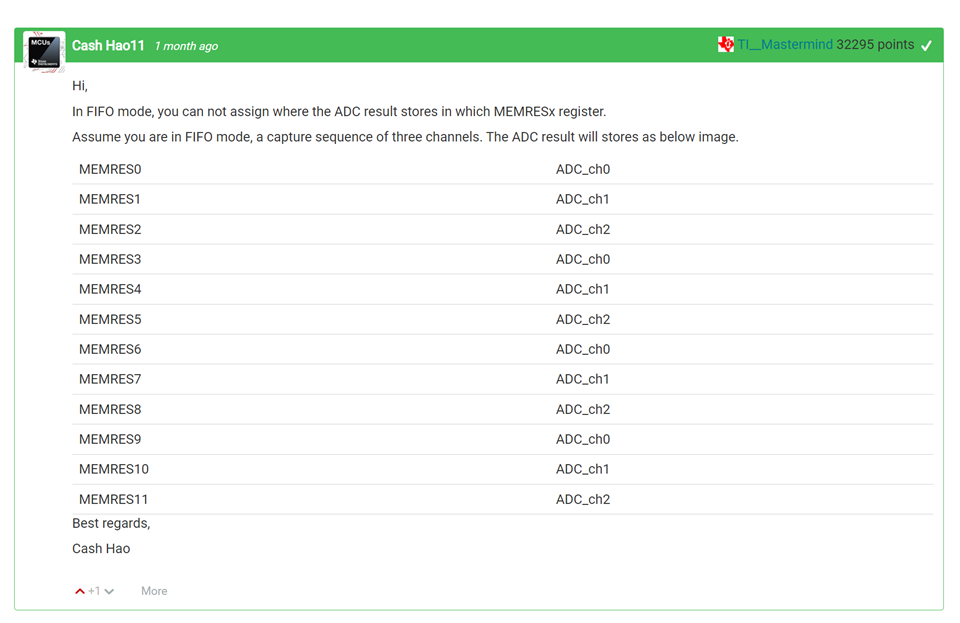

Hello, according to this table, when using the ADC with 4 channels, a DMA, and a FIFO, and toggling an LED each time the DL_ADC12_IIDX_DMA_DONE flag is set, does this mean that the flag will be set when the sampling value is loaded into MEMRES11 and not into MEMRES3?