Other Parts Discussed in Thread: AM2431

Tool/software:

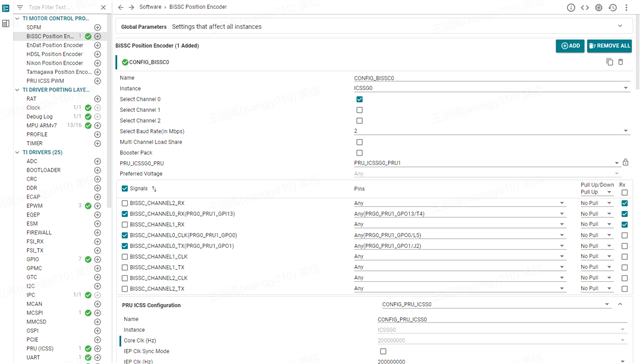

Hi, I am trying to modify from single_chip_servo_am243x-lp_r5ss0-0_nortos_ti-arm-clang to build a demo which can be run on AM2431.

USE_OPEN_LOOP_WITH_SDDF is defined to run open loop with sddf.

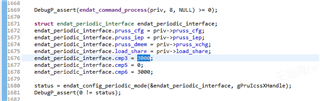

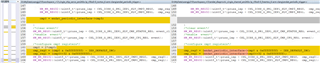

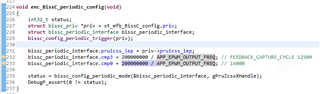

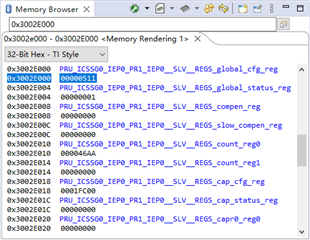

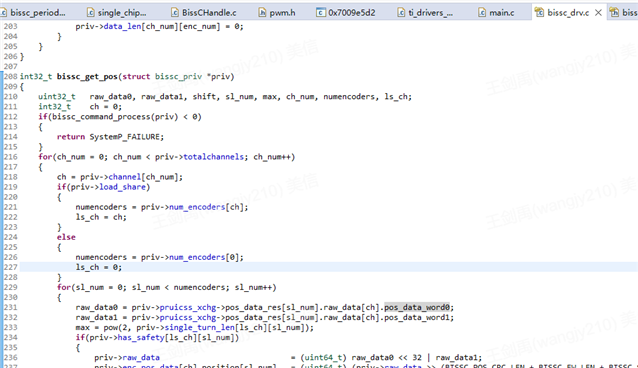

I changed the encoder from ENDAT to BissC (Code is based on BissC single channel diagnostic) using ICSSG0_PRU1.

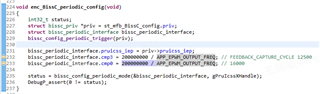

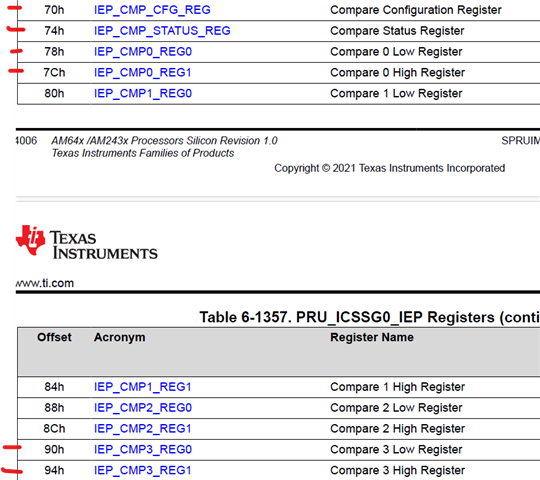

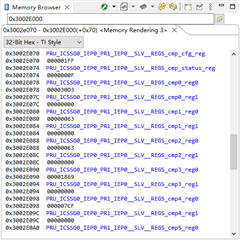

Baudrate is 2Mhz. Core clk and IEP clk is 200Mhz.

IEP clock in Struct SdfmPrms gTestSdfmPrms is also changed to 200Mhz.

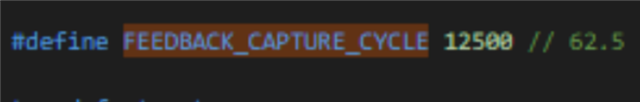

Configured position cycle is 16Khz.

The issue is,

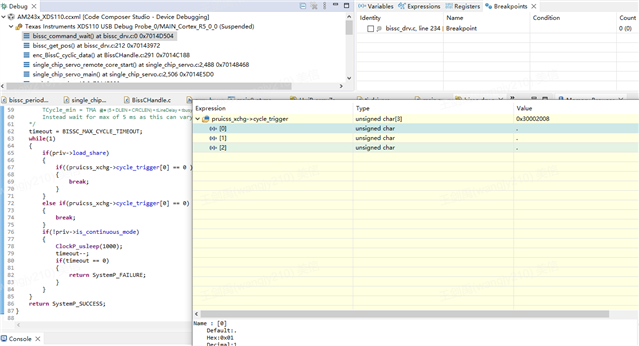

1. The cyclic position is 16Khz if APP_EPWM_OUTPUT_FREQ defined in pwm.h is 4K or 8K.

2. There is no output in clock and data if APP_EPWM_OUTPUT_FREQ is 20k or 50k.

3. The cycle time is around 310 us if APP_EPWM_OUTPUT_FREQ is 16k.

In all 3 test cases, the motor would rotate normally. Position data is available in case 1 and 3, not in case 2.

My question is whether the SDDF and BissC can work in 16Khz with ICSSG0 since ICSSG1 should be used for EtherCAT.

Thanks.

So my goal is to