Tool/software:

The TRM refers to spruim2g.pdf.

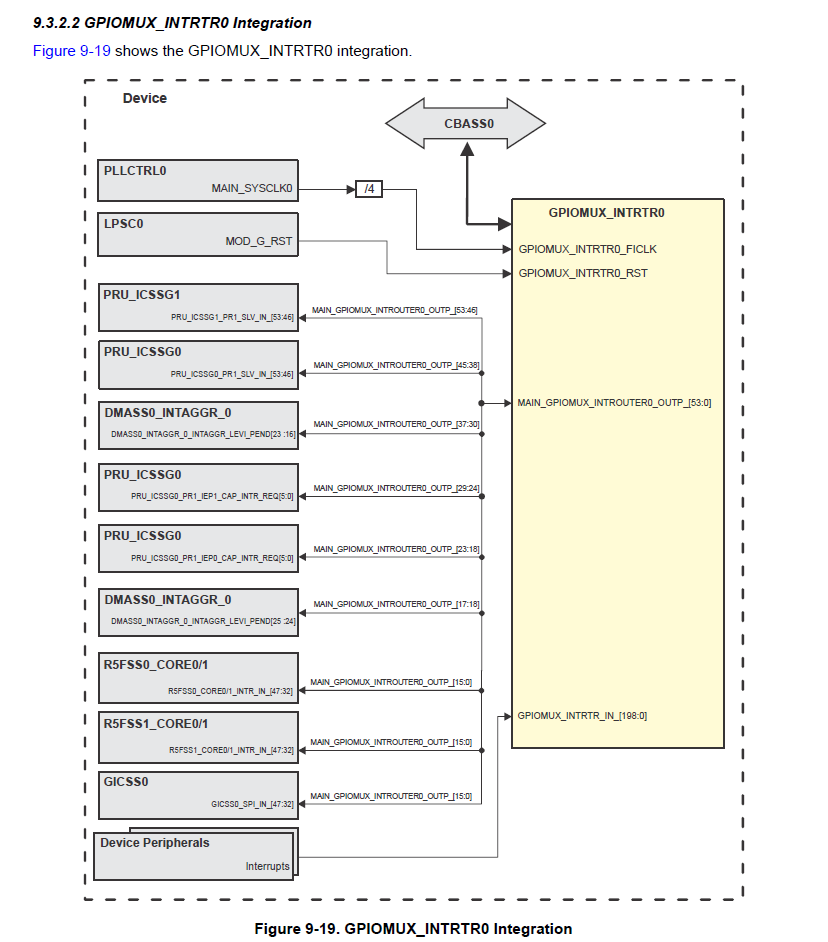

In the explanation of the MAIN domain GPIO interrupt router (GPIOMUX_INTRTR0) in "9.1 Interrupt Architecture" in the TRM, it says "Supported by dedicated MAIN domain GPIO muxing that provides virtualization."

Regarding the above sentence, I am unclear about what "dedicated MAIN domain GPIO muxing that provides virtualization" means.

Therefore, I would like to know the specific details of "dedicated MAIN domain GPIO muxing that provides virtualization."

Thank you in advance.