Tool/software:

Hello,

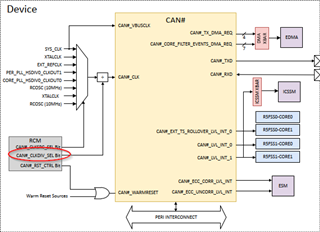

Regarding this picture in the TRM:

Question 1: The register bit field suffix 'CLKDIV_SEL' in the diagram above cannot be found in the Register Addendum. Do you mean this to be: 'CLKDIVR' as shown below in the Register Addendum:

Question 2: If so, what is the coding of the register bit field (CLKDIVR) to actual divider value? According to the description in the excerpt above, the divisor is 8 but I suspect that 1 is added to the register value to give 9 and therefore 9 is the divisor for the input frequency. Is that correct?

Question 3: Are you sure that PLL_CORE_CLK:HSDIV0_CLKOUT0 is 500MHz as shown in the TRM below?

When I debug, it says 400Mhz:

Thank you.