Part Number: TMS570LC4357

Tool/software:

Hello,

I managed to receive CAN data via IF3 with DMA on the TMS570LC4357 microcontroller.

But I am trying to transmit data via IF1/IF2 on CAN using DMA. In this case, I see that DMA does not work.

I came across comments in some of your forum resources that IF1/IF2 registers are in "Privilege Mode" and DMA is in "User Mode", so they are not suitable for sending data.

Can you answer the following questions:

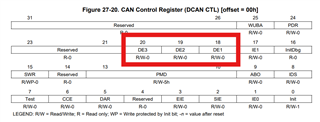

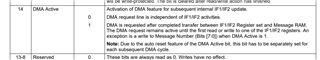

1- Isn't there a corresponding bit in the registers for using IF1/IF2 bits with DMA in the reference document I gave in the attachment? What kind of behavior occurs when I set them?

2- Also, what should I understand from the expression "High Speed Mailbox Access - DMA Access to Message RAM" given in the attachment?

3- Isn't data transmitted via CAN with DMA?

4- If data transmission is not performed, what is the purpose of "DE1/DE2 bits in the CAN Controller Register"?

5- What is the use of "DMA Activate" on the IF1/IF2 CMD register?

6- Privilege mode comment was made for CAN IF1/IF2 Data registers, but when I examined the register, it was seen that it only said "Protected by Busy Bit". In this case, shouldn't I be able to use IF1/IF2 Busy bit with DMA when it is zero?