Other Parts Discussed in Thread: TMDSCNCD263P,

Tool/software:

Hi Team,

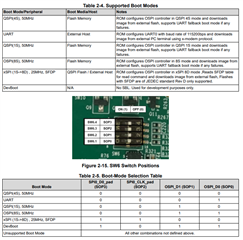

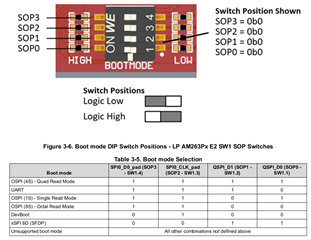

1. TMDSCNCD263P support QSPI 4S/1S boot mode on AM263Px Control Card Evaluation Module User's Guide, but LP-AM263Px haven't QSPI 1S/4S boot mode information on AM263Px LaunchPad User Guide. Therefore, LP-AM263Px support QSPI 4S/1S mode?

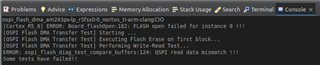

2. I modified OSPI protocol to 1s-1s-1s in ospi_flash_dma example base on SFDP, but the result is an fail. Do I need to modify other configurations?

-

ti_board_open_close.c

/* FLASH DevConfig */

Flash_DevConfig gFlashDevCfg_IS25LX256 =

{

.cmdExtType = OSPI_CMD_EXT_TYPE_REPEAT,

.enable4BAddr = TRUE,

.addrByteSupport = 1,

.fourByteAddrEnSeq = 0xA1,

.cmdWren = 0x06,

.cmdRdsr = 0x05,

.srWip = (1 << 0),

.srWel = (1 << 1),

.xspiWipRdCmd = 0x00,

.xspiWipReg = 0x00000000,

.xspiWipBit = (1 << 0),

.resetType = 0x30,

.eraseCfg = {

.blockSize = 131072,

.sectorSize = 4096,

.cmdBlockErase3B = 0xD8,

.cmdBlockErase4B = 0xDC,

.cmdSectorErase3B = 0x20,

.cmdSectorErase4B = 0x21,

.cmdChipErase = 0xC7,

},

.idCfg = {

.cmd = 0x9F, /* Constant */

.numBytes = 3,

.dummy4 = 0,

.dummy8 = 0,

.addrSize = 0

},

.protocolCfg = {

.protocol = FLASH_CFG_PROTO_1S_1S_1S,

.isDtr = FALSE,

.cmdRd = 0x03,

.cmdWr = 0x02,

.modeClksCmd = 0,

.modeClksRd = 0,

.dummyClksCmd = 0,

.dummyClksRd = 0,

.enableType = 0xFF,

.enableSeq = 0xFF,

.dummyCfg = {

.isAddrReg = FALSE,

.cmdRegRd = 0x00,

.cmdRegWr = 0x00,

.cfgReg = 0x00,

.shift = 0,

.mask = 0x00,

.cfgRegBitP = 0,

},

},

.flashWriteTimeout = 120,

.flashBusyTimeout = 72000000,

};

-

SFDP

================================================

SFDP

================================================

SFDP Major Revision : 0x1

SFDP Minor Revision : 0x9

Number of Parameter Headers in this Table : 4

Types of Additional Parameter Tables in this flash

---------------------------------------------------

4 BYTE ADDRESSING MODE INSTRUCTIONS TABLE

NOR SPI PROFILE TABLE

OCTAL DDR MODE COMMAND SEQUENCE TABLE

Parsing of OCTAL DDR MODE COMMAND SEQUENCE TABLE table not yet supported.

JSON Data for the flash :

{

"flashSize": 33554432,

"flashPageSize": 256,

"flashManfId": "0x9D",

"flashDeviceId": "0x5A19",

"flashBlockSize": 131072,

"flashSectorSize": 4096,

"cmdBlockErase3B": "0xD8",

"cmdBlockErase4B": "0xDC",

"cmdSectorErase3B": "0x20",

"cmdSectorErase4B": "0x21",

"protos": {

"p111": {

"isDtr": false,

"cmdRd": "0x03",

"cmdWr": "0x02",

"modeClksCmd": 0,

"modeClksRd": 0,

"dummyClksCmd": 0,

"dummyClksRd": 0,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": null,

"protoCfg": null,

"strDtrCfg": null

},

"p112": null,

"p114": null,

"p118": {

"isDtr": false,

"cmdRd": "0x7C",

"cmdWr": "0x84",

"modeClksCmd": 0,

"modeClksRd": 1,

"dummyClksCmd": 0,

"dummyClksRd": 7,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": null,

"protoCfg": null,

"strDtrCfg": null

},

"p444s": null,

"p444d": null,

"p888s": null,

"p888d": {

"isDtr": false,

"cmdRd": "0x0B",

"cmdWr": "0x12",

"modeClksCmd": 0,

"modeClksRd": 0,

"dummyClksCmd": 8,

"dummyClksRd": 14,

"enableType": "0",

"enableSeq": "0x00",

"dummyCfg": {

"isAddrReg": false,

"cmdRegRd":"0x00",

"cmdRegWr":"0x00",

"cfgReg":"0x00000000",

"shift":0,

"mask":"0x00",

"bitP":14

},

"protoCfg": {

"isAddrReg": false,

"cmdRegRd": "0x00",

"cmdRegWr": "0x00",

"cfgReg": "0x00000000",

"shift": 0,

"mask": "0x00",

"bitP": 0

},

"strDtrCfg": {

"isAddrReg": false,

"cmdRegRd": "0x00",

"cmdRegWr": "0x00",

"cfgReg": "0x00000000",

"shift": 0,

"mask": "0x00",

"bitP": 0

}

},

"pCustom": {

"fxn": null

}

},

"addrByteSupport": "1",

"fourByteAddrEnSeq": "0xA1",

"cmdExtType": "REPEAT",

"resetType": "0x30",

"deviceBusyType": "0",

"cmdWren": "0x06",

"cmdRdsr": "0x05",

"srWip": 0,

"srWel": 1,

"cmdChipErase": "0xC7",

"rdIdSettings": {

"cmd": "0x9F",

"numBytes": 5,

"dummy4": 0,

"dummy8": 0

},

"xspiWipRdCmd": "0x00",

"xspiWipReg": "0x00000000",

"xspiWipBit": 0,

"flashDeviceBusyTimeout": 72000000,

"flashPageProgTimeout": 120

}

Thanks!

Louis,