Part Number: MCU-PLUS-SDK-AM243X

Other Parts Discussed in Thread: AM2431, UNIFLASH

Tool/software:

Dear TI experts,

I am working on AM2431 board with custom nor flash MT25QL256ABA. I have some problems during nor flash programming.

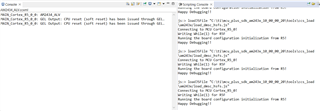

1. I set boot mode to Dev boot and use example project 'ospi_flash_diag_am243x-evm_r5fss0-0_nortos_ti-arm-clang' to get flash parameters.

Save flash parameters to json file and load into project 'sbl_jtag_uniflash_am243x-evm_r5fss0-0_nortos_ti-arm-clang', 'sbl_uart_uniflash_am243x-evm_r5fss0-0_nortos_ti-arm-clang' and 'sbl_ospi_am243x-evm_r5fss0-0_nortos_ti-arm-clang' syscfg.

Then use jtag to debug project sbl_jtag_uniflash, erase, write, verify of flash are success.

After that I change boot mode to QSPI mode, there is no log messages from uart terminal. It seems sbl_ospi doesn't work.

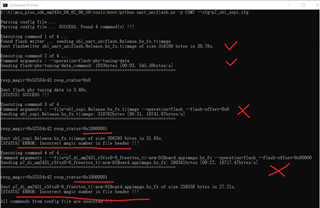

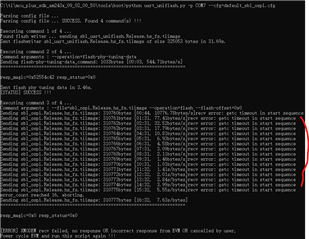

2. I set boot mode to UART, I use python script to download files. 2 of 4 files are transferred fail because of incorrect magic number.

Our DeviceType is HSFS.

I add some information in python script "print("resp_magic={} resp_status={}\n".format(hex(resp_magic), hex(resp_status)))".

I don't know how to continue. Need you help!

Best Regards,

'

'