Tool/software:

Reference's:

MSPM0G Safety Manual SFFS624 03/2024

MSPM0L Safety Manual SFFS619 12/2023

Topic 1: SYSCTL10 External voltage monitor

(Use an external voltage monitor on VCORE pin to monitor the LDO output)

Question 1.1 Fault Detection Failure Modes:

Which Failure Modes need to be monitored (OV-Overvoltage, UV-undervoltage, other-please specify if necessary) ?

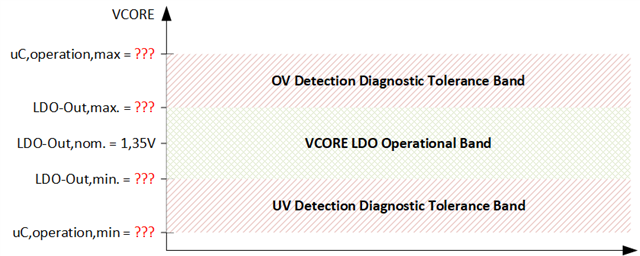

Question 1.2 OV/UV Failure Mode - Fault Detection Bands:

The Data Sheets only specifies the nominal VCORE output voltage by 1.35V. The DS do not specify

- The VORE output Band (min/max voltage output of VCORE)

- The microcontroller operational bands for VCORE.

-> Actually these parameters are necessary, in order to to design UV / OV fault detections

? What is the min/max VCORE LDO output ?

? What is Microcontrollers the min/max operational range of VCORE ?

Question 1.3 OV Failure Mode - Expected Fault Reaction:

What is the expected Fault Reaction, in case the VCORE-OV fault detection trips?

(e.g. VDD shutoff , NRST holding low, other)

Question 1.4 UV Failure Mode - Expected Fault Reaction:

What is the expected Fault Reaction, in case the VCORE-UV fault detection trips?

(e.g. VDD shutoff , NRST holding low, other)

Topic 2: SYSCTL15 External voltage monitor

MSPM0G-SFFS624 (An external voltage supervisor can be used to monitor the power supplies)

MSPM0L-SFFS619 (An external voltage supervisor can be added to the system, which can monitor the VDD line and pull the reset if the VDD is out of expected range.)

Question 2.1 Fault Detection Failure Modes:

Which Failure Modes need to be monitored (OV-Overvoltage, UV-undervoltage, other-please specify if necessary) ?

Question 2.2 UV Failure Mode Coverage by BOR:

Is UV fault detection and reaction already sufficiently covered by BOR (SYSCTL14)?

Question 2.3 UV Failure Mode Coverage by BOR:

What is the expected Fault Reaction, in case the VDD-OV fault detection trips?

(e.g. VDD shutoff , NRST holding low, other)

(within MSPM0L-SFFS619 NRST pulling low is specified. Is the NRST pulling low avoiding silicon pre-damage in case of OV?)

Topic 3: other external Safety Mechanisms required by MSPM0 for ASIL B operational use case

I could not identify other SM requirements on external Safety Mechanisms, that need to be designed by the System Integrator.

Question 3.1

Are other Safety Mechanisms to be externally designed by the System Integrator?

it

it