Tool/software:

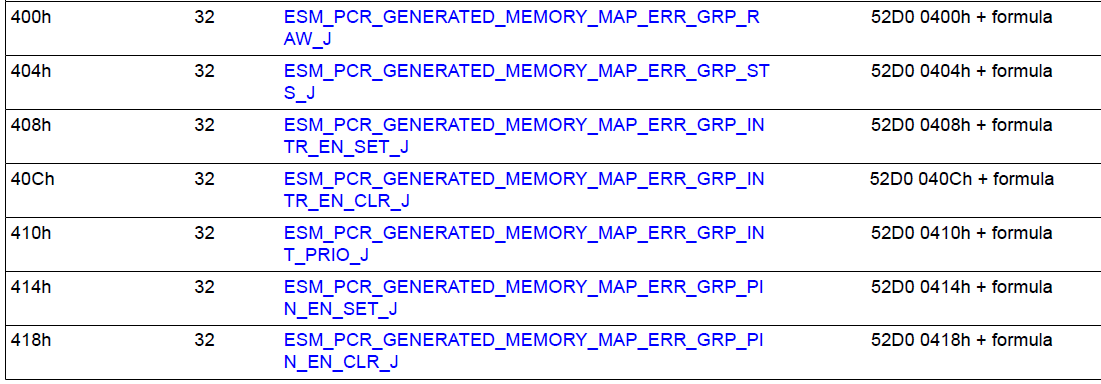

I am trying to enable all ECC and parity-check registers. Looking through the various examples in mcu_plus_sdk_am263x_10_00_00_35\examples\sdl\ecc, there is a ECC_Test_esmInitConfig_MAIN structure in ecc_trigger.c that I believe is enabling the interrupt for the specific ESM fault. The interrupts are enabled by setting bits at addresses 0x52D00428 and 0x52D0042C, yet the latest register addendum ESM register section (in spruj42e) only goes up to 0x52D00418 (in table 5-992). With the latest CCS 12.8 (using CLANG v3.2.2.LTS), my debugger view of registers also ends at this 0x52D00418. Where are the definitions of the registers at 0428 and 042C?

Also 2 additional questions:

1. What are the individual bit-definitions of these ESM registers? The TRM states "Each error event input can be enabled, via software, to cause an Error Interrupt to occur (Error Group N Interrupt Enabled Set Register (Base Address + 0x400 + N*0x20 + 0x08))." -- where are the individual bits defined?

2. Is there a overall acronym list for this processor? I run across acronyms like CSP, MSS, MMR, but searching through the TRM, datasheet, and reg addendum, I cannot find the meaning. It would help to understand this processor if the acronyms were defined.

Thanks,

Jim