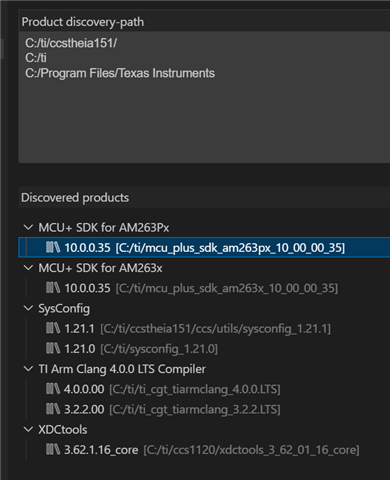

Other Parts Discussed in Thread: AM263P4, LP-AM263P

Tool/software:

Hi

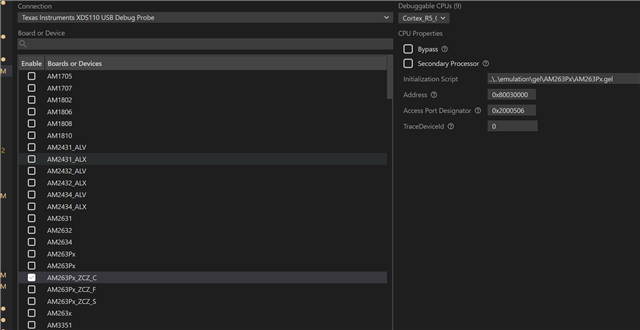

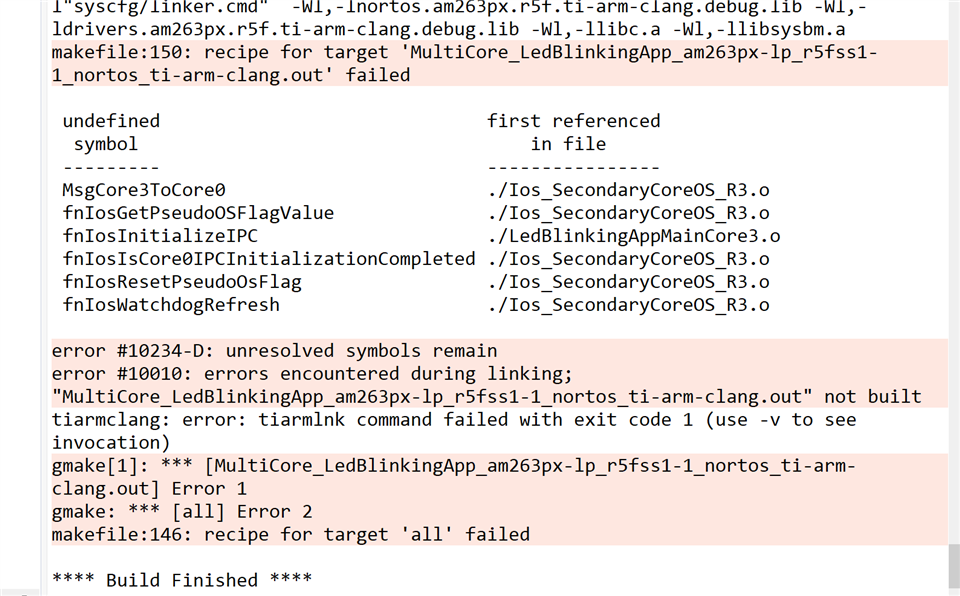

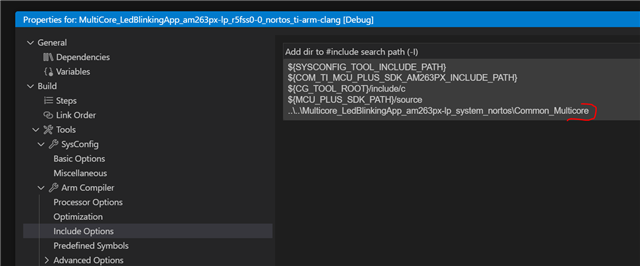

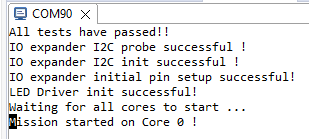

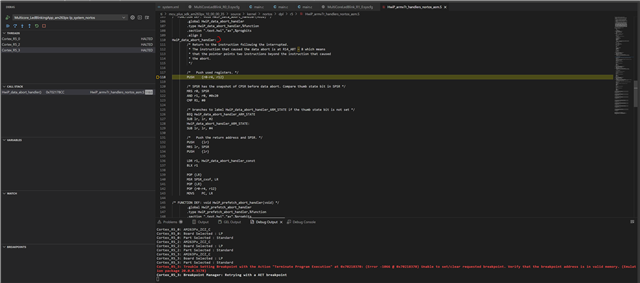

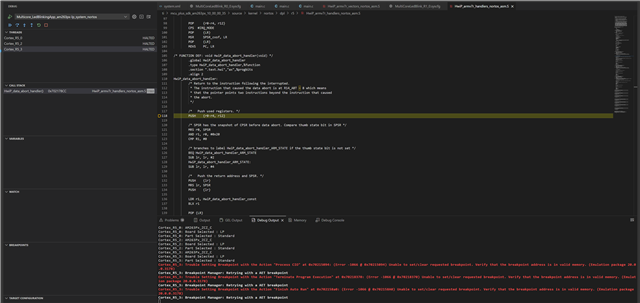

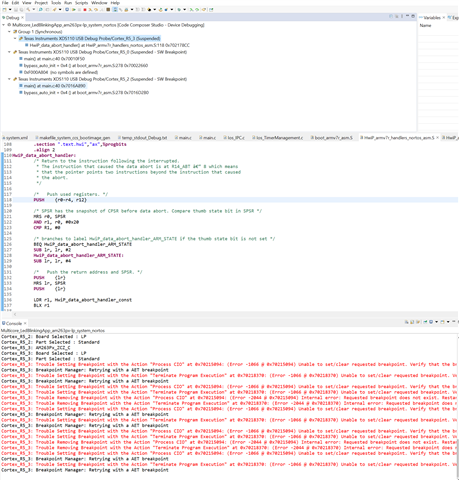

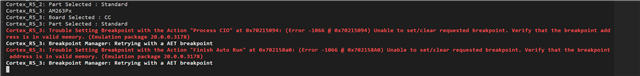

I'm stuck with an issue when CCS is trying to launch a debug session. Screen screenshot below.

The problem arised when updating the application memory mapping to the representative one we intend to use for production.

We have :

Core 0-1 running in lockstep from OCM from 0x70000000 with 1.3MB allocated

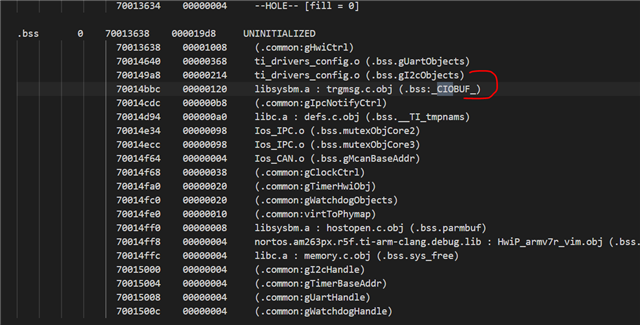

Core 2 running from OCM from 0x70156000 with 684kB allocated

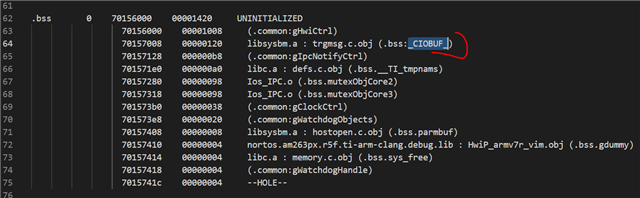

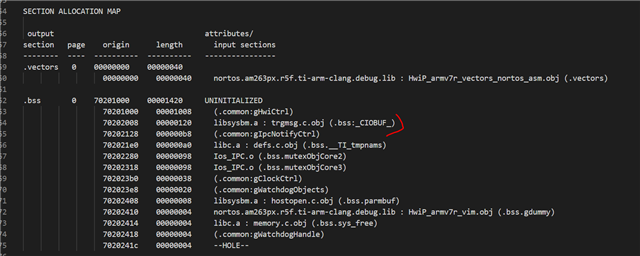

Core 3 running from OCM from 0x70201000 with 684kB allocated

256kBytes empty space for now which reserved for future use.

64kBytes of shared memory starting at 0x702EC000

16kBytes of Shared memory for Debug_log starting 0x702FC000

That mapping is using the 3MBytes of OCM the AM263P4. Linker script reflect this.

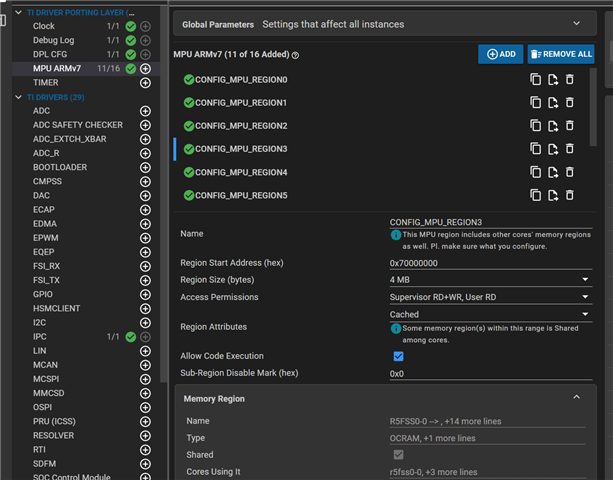

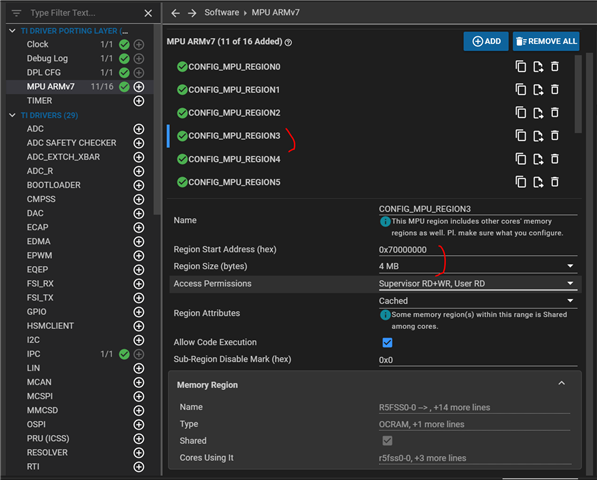

MPU setting have been updated so that all the cores can read write to the shared memory region for now.

MPU setting for each core for OCM is set at

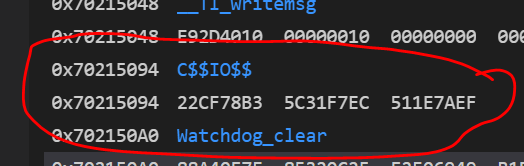

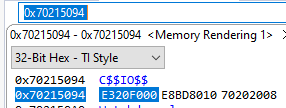

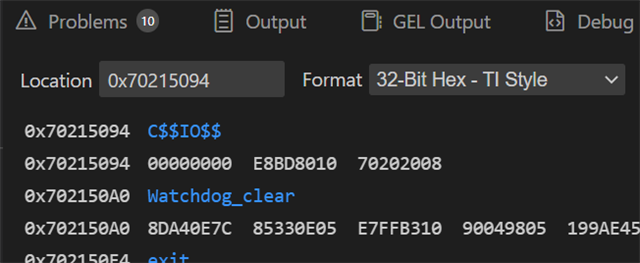

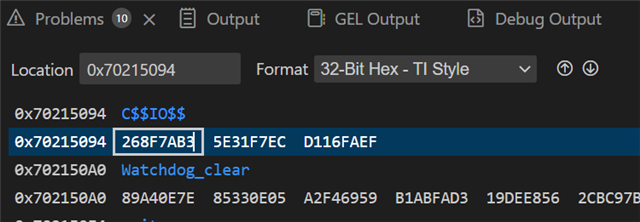

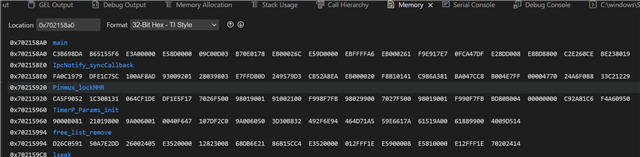

I can see the code loading OK / see screenshot of memory at the address mentioned in the failure message:

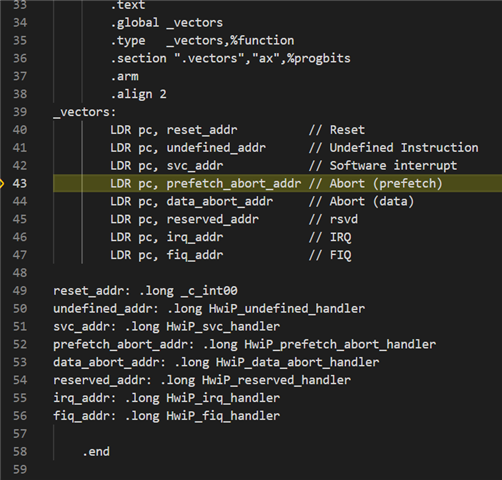

but core R3 always go to a prefetch abort exception:

I can't figure out why.

I've been looking into the gel file to check the CPU memory mapping. I did not seem to find anything relevant.

Could you please point me out into the right direction ?

Thanks

Seb