Other Parts Discussed in Thread: HALCOGEN

Tool/software:

Hi TI gurus,

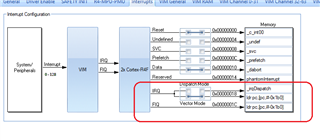

I recently came across this article: NULL pointer protection with ARM Cortex-M MPU. It outlines a clever way to protect from reads/writes to address 0x00 (nullptr) by setting up an MPU region at 0x00 where the MPU prevents all read/writes. The article describes this nullptr protection for Cortex-M but it should hold similarly for Cortex-R, as well as the VIM-based HW interrupt dispatching method implemented on the TMS570. One interesting aspect is that it works on the Cortex-M without moving the vector table (see subheading "What About the Vector Table?" in the article above), which makes it attractive for the TMS570 where the vector table can't be moved.

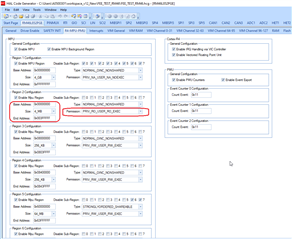

To port to the TMS570, I set up a MPU region from 0x00 - 0x20 (since the interrupt vector is only 32 bytes when using VIM), and declared it as MPU_PRIV_NA_USER_NA_NOEXEC and NORMAL_OINC_NONSHARED.

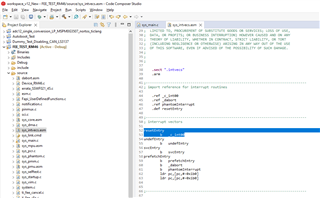

My hope was that this is sufficient to avoid nullptr read/writes, but unfortunately it does not work immediately on the TMS570LC4357 -- I end up with the red ERROR LED and the debugger breaking on or before prefetchEntry in sys_intvecs.asm.

Would anyone know if this method can in fact be ported to the TMS570 and how?

Thanks!