Part Number: AM2432

Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

Hi TI Experts,

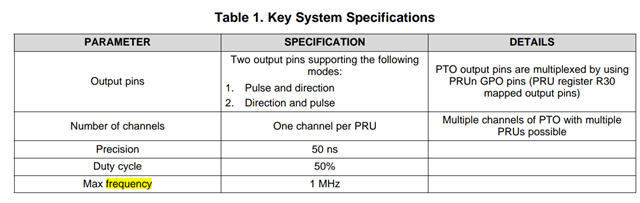

In AM335x, we have a below application note that describes how to perform high performance pulse train output (PTO) with PRU-ICSS.

High Performance Pulse Train Output (PTO) With PRU-ICSS for Industrial Applications.pdf

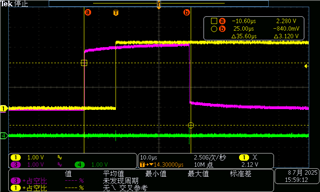

And it could achieve maximum 1MHz outputting pulse + direction.

Customer wants to the similar design on AM243, may I know if it is feasible or not, since we also have PRU in AM243?

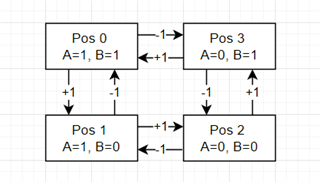

The only difference is that customer outputs pulse + pulse not pulse + direction.

Customer is also wondering if they could achieve higher frequency greater that what we achieved 1MHz in AM335x?

Many Thanks,

Kevin