Tool/software:

Hi TI Experts,

Customer is working on AM2432 SDK9.2.

They are using pin T4 & W3 for EQEP1, and using pin C17 & W4 for EQEP2.

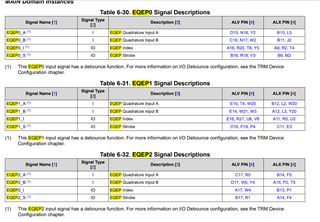

From the datasheet description below, we could know that EQEP1 & EQEP2 both support Debounce feature, which means that pin T4, W3, C17, and W4 support debounce feature.

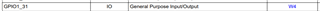

However, when we look at the GPIO session, the pin T4, W3, W4, and C17 stand for GPIO1_23, GPIO1_24, GPIO1_31, and GPIO1_62 respectively shown below.

And below it clearly describes that only for those GPIO who have (1) symbol could support Debounce feature. Unfortunately, all of T4, W3, W4, and C17 do not have (1) symbol.

Actually there are two questions below from customer side.

1: For the same Pin (pin T4, W3, C17, and W4), why it could support Debounce feature when it is configured as EQEP, but not support Debounce feature when it is configured as GPIO? This does not make sense.

2: Could you please double confirm if customer using pin T4 & W3 for EQEP1, and using pin C17 & W4 for EQEP2, could customer use Debounce feature on pin T4, W3, C17, and W4?

Thanks,

Kevin