Tool/software:

Dear expert,

We have encountered a boot up issue with TDA4AL at -40 degree C.

The boot up process hanged and cannot be recovered even we try to reset the PMIC power on process.

The boot process kept the same phenomena unless we warm up the environment.

The failed rate is 5 DUT / 11 DUT = 45%

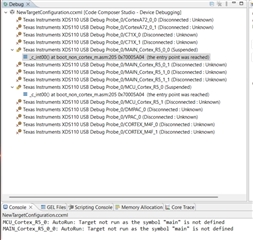

The log we get from the debug console are as following.

Our SW team member has check the code and find the related message.

Please help analyze the reason or the component which may cause the issue.

Thank you

Kevin Kuo