Part Number: AM2434

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi experts,

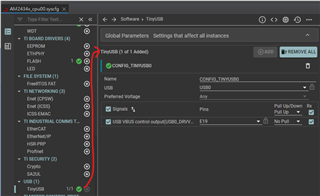

Our team is currently encountering an issue with using TinyUSB communication on the AM2434's R5F0_0 Core (TinyUSB was configured using .sysconfig, as shown in the diagram below).

In our non-OS application with SDK 8.6.0, an external periodic GPIO is used to trigger an IRQ for all cores of the AM2434. On the R5F0_0 core of the AM2434, the priority of this periodic IRQ is higher than the priority of the USB application's IRQ.

For example, if the GPIO trigger period is 62.5 µs, under normal conditions, all cores of the AM2434 will periodically trigger the IRQ function without excessive delay.

However, when the R5F0_0 core is connected to a PC via the USB module, the periodic IRQ trigger time on R5F0_0 occasionally experiences a delay of 7 to 23 µs (based on experimental results). Under the same trigger timing, the other cores of the AM2434 remain precise. Therefore, we believe that certain operations of the USB module are affecting the triggering of all IRQs.

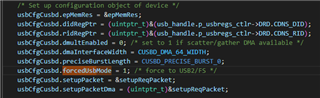

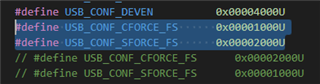

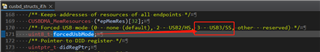

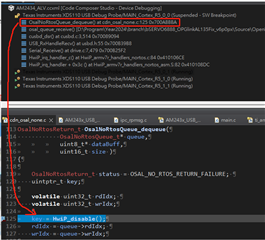

Then, we discovered in the USB source code of SDK 8.6.0 that the original code executes HwiP_disable( ), which disables all IRQs and causes delays in triggering high-priority interrupts.The following describes the two functions:

1. cdn_osal_none.c - OsalNoRtosQueue_enqueue( )

2. cdn_osal_none.c - OsalNoRtosQueue_dequeue( )

We tried rewriting the two functions and removing HwiP_disable(), but the issue still persists.

Besides these two functions, we would like to know if there are any other operations in the USB source code that execute actions similar to HwiP_disable() or Semaphore_Pend(), which could cause all interrupt triggers to be disabled."

The following lists the functions from SDK 8.6.0 that are currently used in our program :

- usb_wrapper.c

- usb_irq6_isr( )

- cusbd.c

- cusbd_dsr( )

- usbd.h

- tud_task( )

- cdc_device.c

- tud_cdc_n_available( )

- tud_cdc_n_read( )

- tud_cdc_n_read_flush( )

- tud_cdc_n_write_available( )

- tud_cdc_n_write_flush( )

- cdc_device.h

- tud_cdc_n_write_char( )

Could the experts help review the functions listed above and let us know which functions need to be modified, or provide other suggestions to resolve this issue?

Regards

Bolt