Tool/software:

Hi,

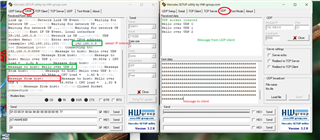

Anyone can please help in solving the below problem. While trying to establish a TCP/UDP connection we are able to form a connection but not able to receive the data. We are using the sample program from resource Explorer.

|

1 |

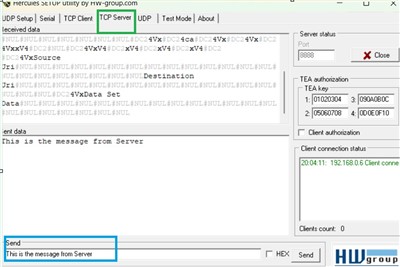

TCP testing: when we run the TCP client example, we are able to receive the data to server., But, in receiving data from the server, we are not able to access the receive buffer:

struct netbuf *rxBbuf = NULL;

(we could not find the structure of “netbuf”, so we are unable to access the “receive buffer data” over TCP) |

|

2 |

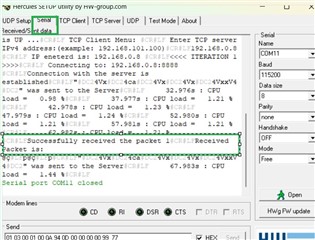

UDP testing: UDP data is being received at server side but unable to receive data from server. What are the functions to be called for UDP socket Open, send/receive data and close the socket, in the same TCP client App? We need to run both UDP and TCP to send/receive data on both the sockets at a time.

|

In the code section of UDP client:

We did not receive the data to “gRxDataBuff “ sent from server:

ret = lwip_recvfrom(sock, gRxDataBuff, APP_SOCKET_MAX_RX_DATA_LEN, 0, pAddr, &len);

gRxDataBuff[ret] = '\0';

EnetAppUtils_print("Message from host: %s\r\n", gRxDataBuff);