Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

My customer is evaluating AM263P4 with below environments.

CCS : 12.8.1

SDK : 10.1.0.31

SYSCONFIG : 1.22.0

Board : TMSDCND263P (AM263Px controlCARD)

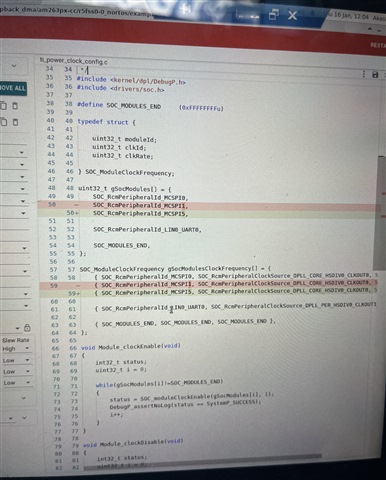

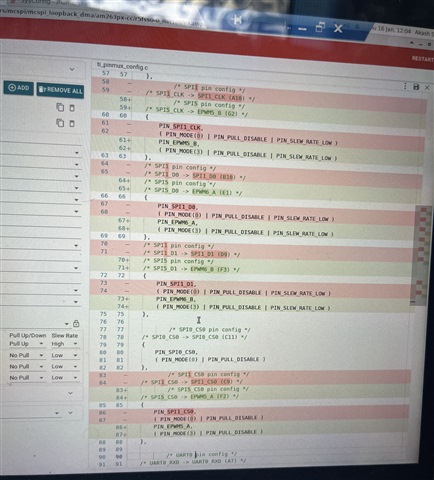

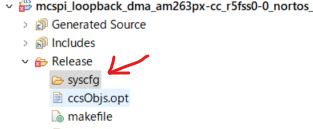

He wants to evaluate MCSPI5, so uses "mcspi_loopback_dma_am263px-cc_r5fss0-0_nortos_ti-arm-clang" project as a staring point.

The default project works properly with MCSPI0.

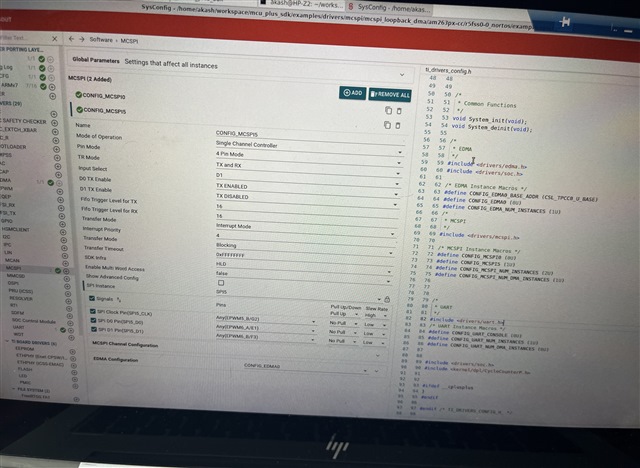

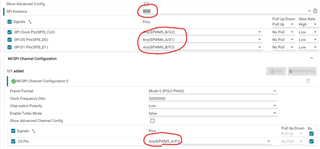

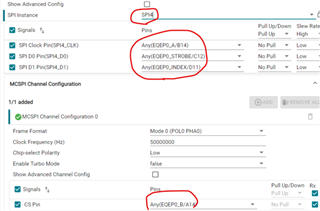

Now he tried to change MCSPI0 to MCSPI5 in SYSCONFIG like below.

With this configuration, SYSCONFIG did not generate any code, so build failed.

Building file: "../example.syscfg"

Invoking: SysConfig

"C:/ti/sysconfig_1.22.0/sysconfig_cli.bat" --script "C:/Users/xxxxx/workspace_v12/yyyyy/mcspi_loopback_dma_am263px-cc_r5fss0-0_nortos_ti-arm-clang_org/example.syscfg" -o "syscfg" -s "C:/ti/mcu_plus_sdk_am263px_10_01_00_31/.metadata/product.json" --context "r5fss0-0" --part AM263P4 --package ZCZ_S --compiler ticlang

Running script...

Validating...

info: CONFIG_MPU_REGION3(/kernel/dpl/mpu_armv7) attributes: Some memory region(s) within this range is Shared among cores.

info: /kernel/dpl/debug_log uartLog.baudRate: Actual Baudrate Possible: 115385 (0 % error)

Generating Code (example.syscfg)...

subdir_rules.mk:9: recipe for target 'build-1900555631' failed

TypeError: Cannot read properties of undefined (reading 'path')

at subTemplateFunction (C:\ti\mcu_plus_sdk_am263px_10_01_00_31\source\sysconfig\xbar\.meta\dma_trig_xbar\templates\dma_trig_xbar_open_close_config.c.xdt:48:56)

at C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\resources\runtime.ts:114:11

at templateFunc (C:\ti\mcu_plus_sdk_am263px_10_01_00_31\source\sysconfig\drivers\.meta\system\drivers_open_close.c.xdt:162:66)

at func (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\codeGeneration\templateRunner.ts:29:39)

at allowPathVisibility (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\pathsVisibility.ts:11:10)

at runTemplate (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\codeGeneration\templateRunner.ts:29:13)

at t.CodeGenerator.generate (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\codeGeneration\codeGenerator.ts:136:10)

at iteratee (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\src\pinmux\services\codeGeneration\codeGenerator.ts:141:26)

at baseMap (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\node_modules\lodash\lodash.js:653:23)

at Function.wa [as map] (C:\ti\sysconfig_1.22.0\dist\webpack:\sysconfig\node_modules\lodash\lodash.js:9621:51)

gmake: *** [build-1900555631] Error 1

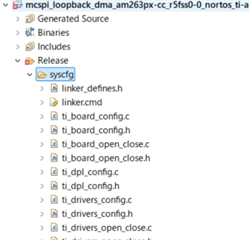

gmake: Target 'all' not remade because of errors.In case other MCSPI, such as MCSPI4 is selected, codes are generated as expected.

It seems a bug in SYSCONFIG.

Thanks and regards,

Koichiro Tashiro