Part Number: LP-MSPM0L1306

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi TI,

I am trying to use comparator output to trigger ADC sampling. This part works. But I need to disable the sampling at certain time during my application. When re-enable the sampling back, the adc samples incorrect result.

Here is how to replicate the problem on LP-MSPM0L1306.

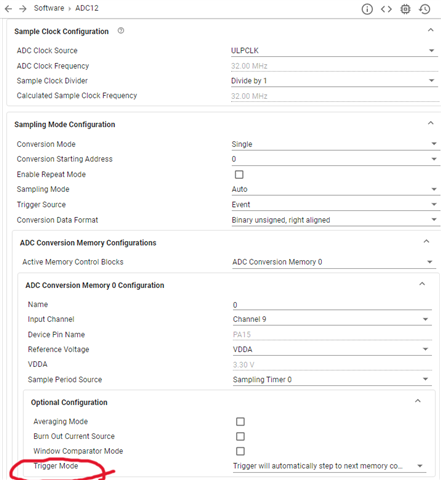

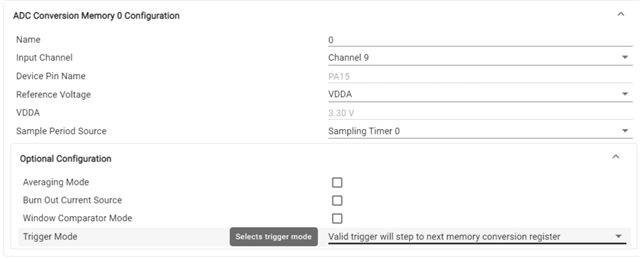

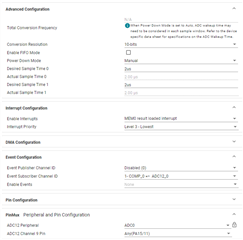

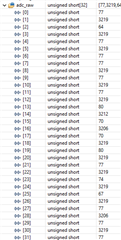

Sysconfig(see attached photo):

Use PWM to generate 1khz, 50% duty cycle square wave at PA3

Set comparator to use PA26 as positive input, internal voltage reference as negative input. generate event signal with DL_COMP_EVENT_OUTPUT_EDGE to trigger ADC

Set ADC to event trigger, single conversion, disable repeat mode, sample PA15

Connect to comparator positive input and ADC channel.

Connect PA3, PA15, PA26 together on board

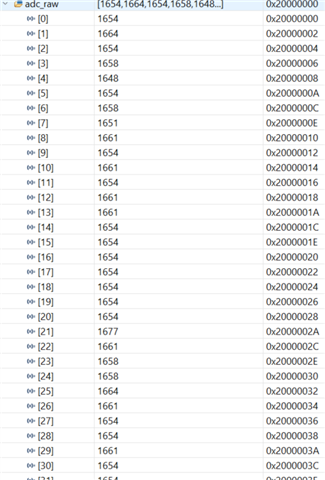

Run the code attached in debug mode, it should stop after 5 second, adc_raw buffer will be filled with 3300. This is correct because when ADC samples, PWM is at logic high.

#include "ti_msp_dl_config.h"

#include "main.h"

volatile uint16_t adc_raw[32];

volatile uint8_t debugCnt=0;

void record_ADC_res(){

uint16_t res = DL_ADC12_getMemResult(ADC12_0_INST, DL_ADC12_MEM_IDX_0);

adc_raw[debugCnt]=res*3300/1023;

debugCnt++;

if(debugCnt>=32) {

debugCnt=0;

__BKPT();

}

}

bool adcTriggered=false;

int main(void)

{

SYSCFG_DL_init();

for(uint16_t i=0;i<5000;i++){

delay_cycles(32000);//1ms delay

}

DL_COMP_enableEvent(COMP_0_INST, (DL_COMP_EVENT_OUTPUT_EDGE));

DL_ADC12_enableConversions(ADC12_0_INST);

NVIC_EnableIRQ(ADC12_0_INST_INT_IRQN);

while (1) {

if(adcTriggered){

adcTriggered=false;

record_ADC_res();

//DL_COMP_disableEvent(COMP_0_INST, (DL_COMP_EVENT_OUTPUT_EDGE));

//delay_cycles(32*1500);

//DL_COMP_clearEventsStatus(COMP_0_INST, (DL_COMP_EVENT_OUTPUT_EDGE));

//DL_COMP_enableEvent(COMP_0_INST, (DL_COMP_EVENT_OUTPUT_EDGE));

DL_ADC12_enableConversions(ADC12_0_INST);

}

}

}

void ADC12_0_INST_IRQHandler(void)

{

switch(DL_ADC12_getPendingInterrupt(ADC12_0_INST))

{

case DL_ADC12_IIDX_MEM0_RESULT_LOADED:

adcTriggered=true;

break;

}

}

Then, uncomment the "delay_cycles(32*1500);". This simulate disabling the sampling because adc conversion will only be enabled after this delay.

When running the code, you can see the result sometimes become logic 0.

My question is:

- What cause the adc to sample the wrong value?

- How to configure the ADC, or comparator, or event correctly, so the sampling result will still be correct after re-enable the sampling

Note that I cannot use PWM to trigger ADC, because PWM is just to simulate an external signal for easy troubleshooting.

I am using CCS 12.8.1, sysconfig 1.21.0, sdk 2.2.0.05

I appreciate your prompt response. Thank you!