Tool/software:

Dear SupporTeam,

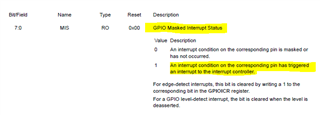

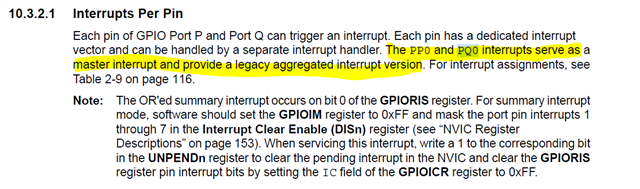

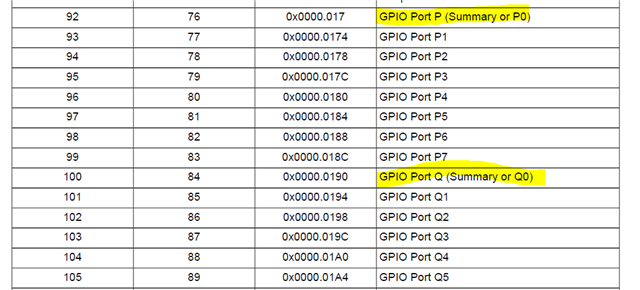

not clear with highlighted text, what's the meaning of master interrupt, what's legacy aggregated interrupt version? If we are going to use PQ0 pin as an digital i/p interrupt pin. do we need to handle differently?

Thank you.

Regards

Abhijit