Part Number: MSPM0L1305

Tool/software:

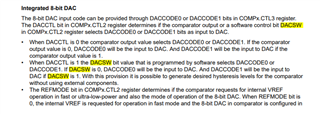

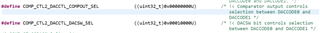

In order to let the COMP output control the selection between DACCODE0 and DACCODE1 (for hysteresis), the DACCTL bit in CTL2 should be 1 according to Sect. 15.2.8 but 0 according to Sect. 15.3.24. Which one is correct. I already have submitted document feedback.