Other Parts Discussed in Thread: SYSCONFIG, SEGGER

Tool/software:

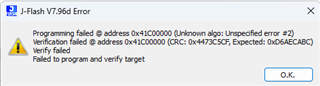

I am trying to restrict the SW Debug Access using a password. However, when I flash the device using JFlash 7.96 I receive the following issue concerning the CRC value in NONMAIN:

Steps to Reproduce:

1. Set the Serial Wire Debug lock policy according to 1.5.2

2. Set SWD Password according to 1.5.4

As a test, I am using a dummy password: 00010203 04050607 08090A0B 0C0D0E0F

3. Here are the values in the compiled image at the correct addresses:

4. Try to erase the device but fail because NONMAIN sector is locked

5. Try to program the device device but CRC is incorrect

6. Tried to reverse engineer the default CRC32 digest value found at 1.5.15 but it's pretty much impossible to do if you don't know which address range or exact algorithm scheme you guys are using.

Questions:

1. How do you erase NONMAIN using JFlash without bricking the device?

2. Which exact address range(s) is being used to calculate the CRC for the BCR and BSL respectively?

3. Which exact CRC32 algorithm are you using to calculate the checksum?

4. How does TI expect us to calculate these CRC values ourselves?

5. We want to randomize the password and automate the process during CI/CD deployment, is there a python library/script you recommend that uses the same exact CRC scheme? If not, how would we be able to randomize the password, and then when compiling/linking populating those fields with the randomized words?