Tool/software:

The OSPI is connected to the FLASH memory and is used with a single I/O bus.

OSPI only reads during boot.

The program is designed to write USB data to the FLASH memory only when a USB is inserted.

Currently, since no USB is inserted, there is no access after boot.

In this state, if the power is turned off, there may be OSPI access.

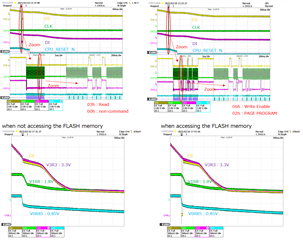

I checked the commands sent to FLASH memory with an oscilloscope during power-off.

In most cases, the command is a Read command (03h) or a (00h).

Very rarely, a Write Enable command (06h) and PAGE PROGRAM command (02h) are sent.

Since the PAGE PROGRAM happens during power-off, the power is cut off midway, and the data in the FLASH memory gets corrupted.

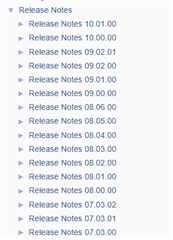

There seems to be no difference in the power supply voltage when accessing the FLASH memory or not during power-off.

Q1. Is it unavoidable for the CPU to malfunction and access the FLASH memory during power-off?

It is not a problem if the Read command is executed during power-off. However, I want to avoid the execution of the PAGE PROGRAM.

Q2. Is there a way to avoid this?