Part Number: MSPM0L1306

Tool/software:

Appreciate any advice for this:

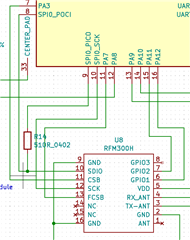

I am connecting to a CMOSTEK CMT2300A RFM300HW HopeRF module. I have to contend with (ref P27/46 CMT2300A_EN_V1.0 manual) "To be noticed, when reading a register, MCU and CMT2300A will have to switch the direction of their IO (SDIO) between the address bit 0 and the data bit 7. It is required that the MCU switches the IO to input mode before send out the falling edge of the SCLK; CMT2300A should switch the IO to output mode after it has seen the falling edge of the SCLK. This avoids data contention of the SDIO (both of the MCU and CMT2300A set the SDIO to output mode at the same time), which would cause unexpected electrical problem."

I have a resistor R14 on the CPU Controller Out line to try and save burning out should the RF module and CPU decide to drive out at the same time.

Excluding bit banging everything, what would be the best way to make this work? I manually drive the SPI chip select(s) in software so it stays enabled as long as I like.

1. Create a timer interrupt that is just shy of the of the time the last bit finishes transmitting, and reconfigure the SPI_PICO pin to an input so it stops driving before the SPI_CLK transitions to enable the RF module to start TX

2. When sending the SPI_PICO register address from the CPU to the RF module, set the frame format to 7 bits to send bits 7 to 1, and then handle the last bit separately in software by re configuring the SPI pins as GPIO and bit banging the last bit before changing to read the register data?