Tool/software:

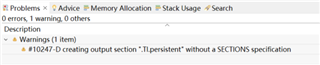

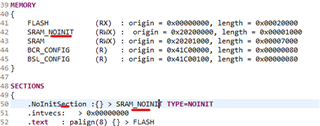

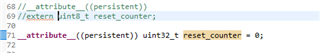

When I use the "persistent attribute" on MSPM0G3507, I see that the variable is allocated in the SRAM and is re-initialized to 0 at RESET or startup:

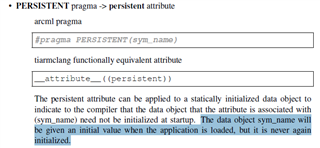

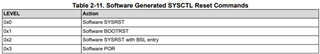

I want to know if there is any method on the MSPM0G that allows a variable to be not zero-initialized at startup or reset, similar to the persistent attribute works on the MSP430FR.

Thanks and Regards,

SON.