Part Number: LP-MSPM0G3519

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Team,

I have the example case provided by TI which reads/writes 0x00001000 address.

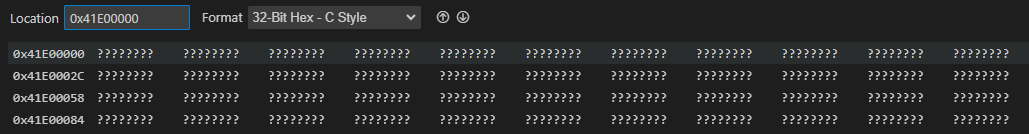

Now want to try program and read from 0x41E00000 region.

While trying to change it to write starting from 0x41E00000 using the available functions from SDK i am not able to write.

Memory shows ???? in the memory view of CCS, how to use this memory for write and read operations?

Please support to resolve this

Thanks.