Tool/software:

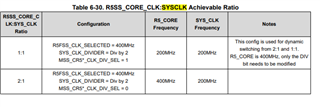

In all the PWM examples the EPWM is 200MHz (XTAL=25MHz, DPLL_CORE_HSDIV0_CLKOUT0=400MHz, SYS_CLK=200MHz).

Why is SYS_CLK not at 400MHz? Please help address the following questions:

- Is there any restrictions on setting SYS_CLK to 400MHz? (Set SYS_CLK_DIVIDER = Div by 1)

- How can I set SYS_CLK to 400MHz?

- Do I need to have a new SBL?

- For completeness, is there any reason why EPWMCLK can not be 400MHz as well?

Other related questions:

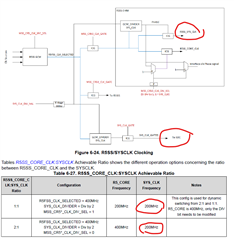

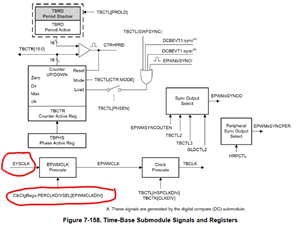

- On Figure 7-158 of TRM, which SYSCLK is EPWMCLK derived from? See Figure 6-24

- R5SS_SYS_CLK or SYS_CLK_GATED.

- On Figure 7-158, where can I find the register "ClkCfgRegs.PERCLKDIVSEL[EPWMCLKDIV]" to configure the EPWMCLK Presacle?

- None of the tokens/words can be found from searching SDK code and Register Addendum.pdf

Providing some pictures for my question to help.

Thanks for the support.