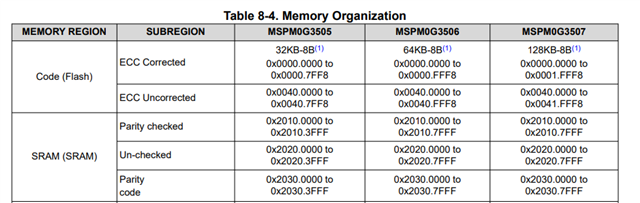

Part Number: MSPM0G3507

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi there,

I would like to implement CAN RX with DMA.

Is there any corresponding documentation, tutorials, sysconfig, code examples that I can refer to and learn from?

Unfortunately I have not found much suitable.

Thanks a lot in advance.

Matze