Tool/software:

Hi,

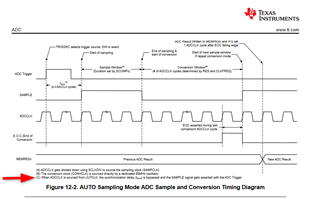

I configured the available external oscialltor on the Launchpad to be the ADC clock source (HFCLK - 40Mhz). It is only sourcing the ADC, the source of the MCLK is SYSOSC. When changing the clock source of the ADC from ULPCLK to HFCLK, the calculated sampling rate goes down in CSS Theia. I assume is due to the additional 2-3 clock cycles for sync when not using ULPCLK.

I did a test measurement and noticed that the actual sampling rate is not as given by CSS Theia, but higher matching exactly the value given when ULPCLK is used.

I'm sure that in general the external oscialltor is used, since the time base is far more accurate compared to ULPCLK with SYSOSC.

Any ideas?