Part Number: AM2634

Tool/software:

Hi!

I now have a question about the MCAN ECC configuration to consult,I will describe the phenomenon of the problem below。

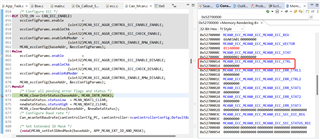

In my program, I execute can_init first and then SDL ECC Config. There is code in can_init to Enable or Disable ECC, which affects the SDL's ECC configuration. Below I use the demo program to simply explain the problem phenomenon.

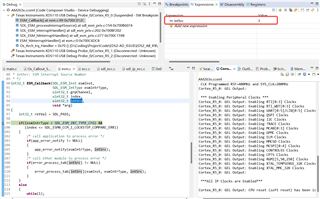

① The first case

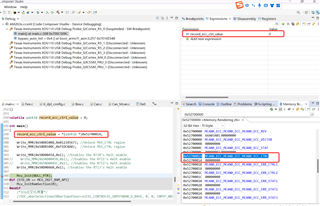

I use *(volatile uint32_t *)0x52700014 = 0; Code to simulate the MCAL CAN ECC Disable operation. You can see from the following figure that after SDL ECC initialization is complete, the value of MCAN0_ECC_CTRL is still 0.

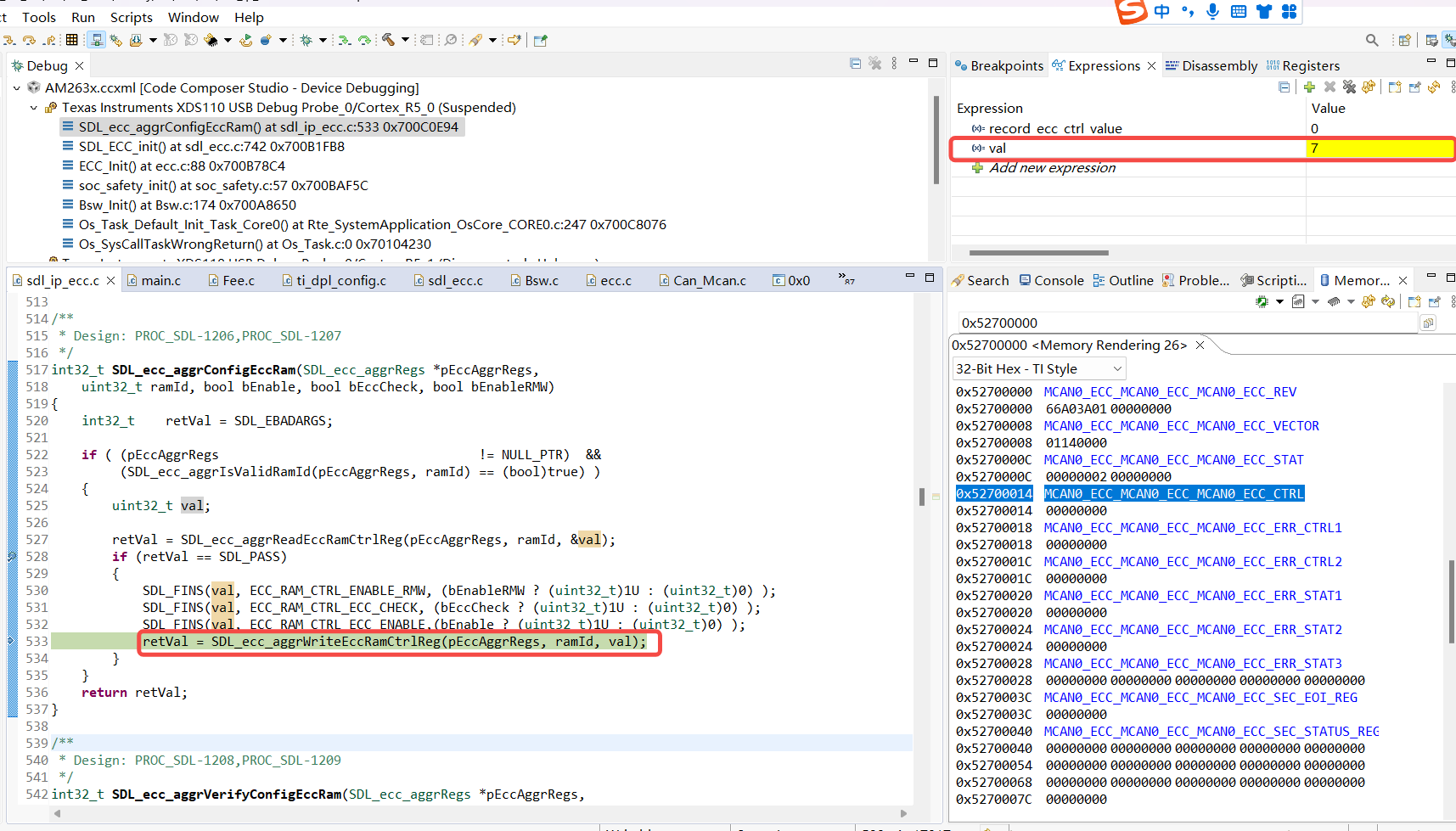

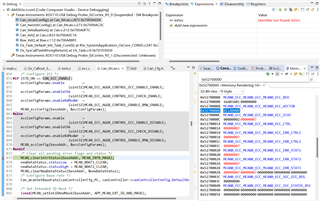

② The second case

I use *(volatile uint32_t *)0x52700014 = 7 Code to simulate the MCAL CAN ECC Enable operation. You can see that the value of MCAN0_ECC_CTRL is 7 after the SDL ECC initialization is complete.

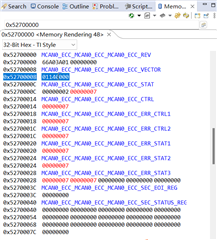

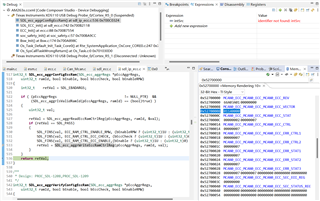

③ The third case

Perform only SDL ECC initialization, and you can see that the value of MCAN0_ECC_CTRL is 0x187 after initialization.

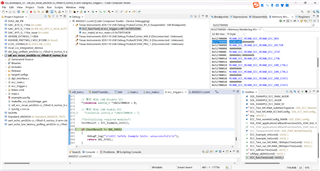

I did tests on all three, and the first one had an exception, the second and third worked fine.

In my program, the MCAL CAN module performs Disable ECC, using the first case. In this case, when the CAN driver receives a Message, ECC faults will be triggered and the CAN driver will be stopped.

I would like to know why the MCAL MCAN ECC configuration affects the SDL MCAN ECC configuration. I need to Enable MCAL MCAN ECC Enable? Or do I mask the MCAL MCAN ECC Config code?