Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi TI experts,

We are having trouble connect our drives (AM2432) to KEYENCE KV7500 PLC. But our other products (Infeneon XMC4800) are OK.

The issue is that,

1. If KV7500 is connected to only 1 AM2432, drive can switch to OP.

2. If KV7500 is connected to AM2432, then some other drive(AM2432, XMC4800 or drives from other company), AM2432 would not pass the frame to XMC4800.

From the video the IN port from left is blinking, but OUT port is not. The network analyzer is put between two drives, and nothing is captured.

3. If KV7500 is connected to XMC4800, then AM2432, AM2432 would not return any frame on first connection.

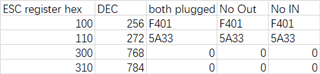

The network analyzer is put between KV7500 and XMC4800, the captured result is attached.

KV7500_CDHD2_CD3E_no_return_first.zip

Furthermore, after the connection, XMC4800 can be connected to KV7500 if AM2432 is removed.

AM2432 needs a power cycle to be able to connect to KV7500.