Part Number: TM4C129XNCZAD

Other Parts Discussed in Thread: TEST2

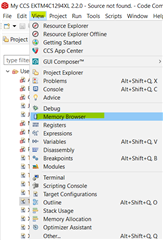

Tool/software:

Dear Sir,

We used Ti based flash based booloader exmplae. We have modified the bl_config.h for UART based interface update.

It is working also. We used UART1 ,baud rate 115200 and LM flash loader to update the application.

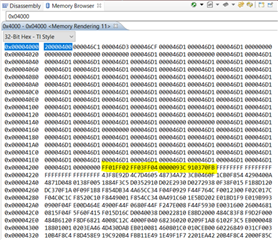

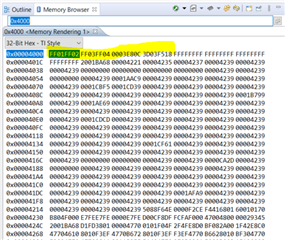

Now question is that if we interrupt the process of LM flash loader update in between then not able to update again.

and device also not bootup after restart.

What more setting to be do in bl_config.h like CRC check etc. To avoid this condition.

CRC_Check is sufficient to make device retain old code.