Part Number: AM2432

Tool/software:

Hi ALL:

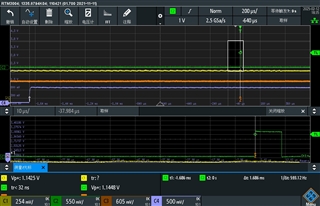

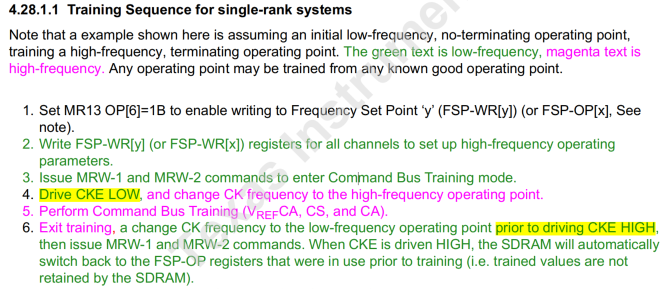

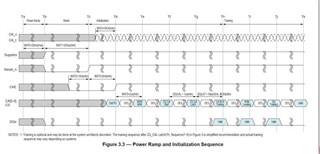

Our project AM2432 external expansion RAM is LPDDR4 model: IS43LQ32256B-062BLI & ISSI , We found that the CKE signal of DDR has a brief high pulse signal (10us) after being pulled high by Reset-n during the testing of the DDR "Power Ramp and Initialization Sequence" Inconsistent with LPDD4 manual, please help confirm the cause of the signal and whether it is reasonable.

Note:

Figure 1 LPDDR4 Power Ramp and Initialization Sequence

Figure 2 Actual test waveform of Power Ramp and Initialization Sequence oscilloscope

Figure1 LPDDR4 Power Ramp and Initialization Sequence(from datasheet)

Figure 2 LPDDR4 Power Ramp and Initialization Sequence(we test scope)