Tool/software:

Hi all,

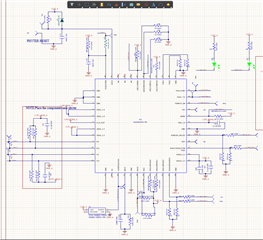

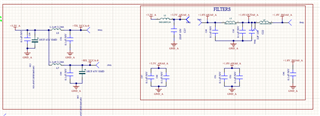

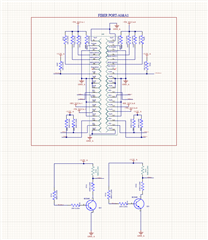

In our custom design with AM2634 we implemented an ethernet circuit using phyther KSZ8041FTLI-TR, while we are testing this circuit, we observed some issues in data transmission and reception, we are losing some packets while transmitting and receiving packets, so we tested using far end loop back and near end loop back, if far end loop back i.e switch to phyther loop back no packets were missing but while testing between controller to phyther we observed data miss some packets are getting missed. please help us to resolve the issue