Tool/software:

Hi,

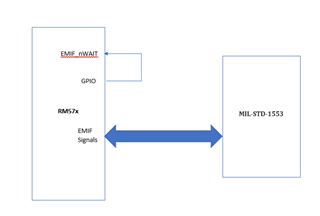

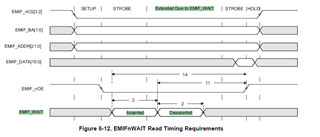

I previously posted a thread regarding the EMIF and MIL-STD-1553 bus interface. I am planning to use the EMIF_nWait signal to manage the timing between the GPIO control lines and the EMIF lines.

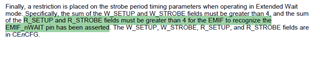

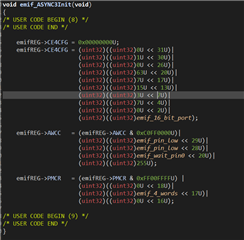

EMIF Configuration:

- EW bit is set to 1 in the CE4CFG register.

- WP0 and WP1 bits are set to 0 in the AWCCR register.

- CS4_WAIT bit is set to 0 in the AWCCR register.

- MAX_EXT_WAIT is set to 255 in the AWCCR register.

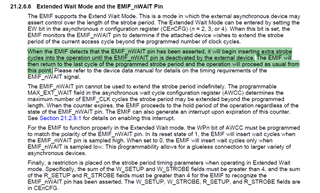

The write operation works fine when the EMIF_nWait signal is used to extend the write operation. However, during the read operation, the system enters a data entry abort interrupt when EMIF_nWait is asserted low. The EMIF_nWait signal is controlled by GPIO. If I keep EMIF_nWait high, I can read the value correctly, but when I set it low, the operation fails.

And also I tried in Select Strobe mode but result is same. It enter into dataEntry abort.

A similar issue was discussed in the following thread, but the problem remains unresolved:

e2e.ti.com/.../rm57l843-emif-in-asynch-mode-with-extended-wait-needs-clarification

Could you please provide guidance on resolving this issue?

Thanks,

Regards,

Veerappan P.