Part Number: AM2432

Other Parts Discussed in Thread: TDA4VH

Tool/software:

Hi TI Experts,

Customer is working on AM2432 SDK9.2.

Customer is okay to only connect 1 core like R50-0 to debug on CCS with no problem shown below.

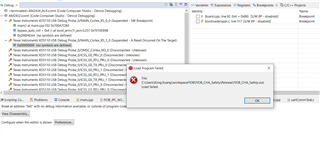

However, if customer wants to debug an additional core like R51-0 on CCS (when R50-0 is already connected), they will have the below problem.

The details of this problem is showing below.

May I know could you provide some guide to help customer run multi-core debug on CCS please?

Thanks,

Kevin