Part Number: AM263P4-Q1

Tool/software:

Hello,

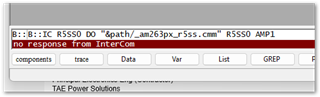

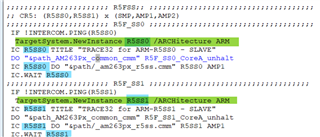

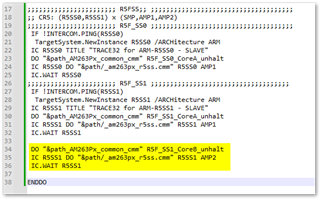

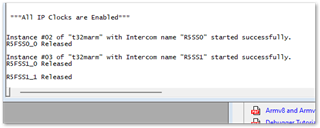

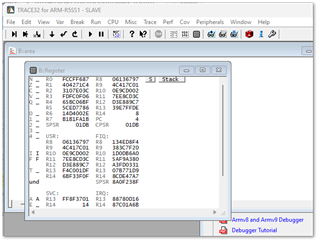

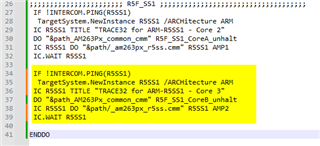

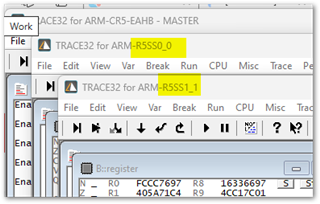

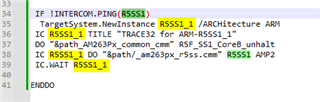

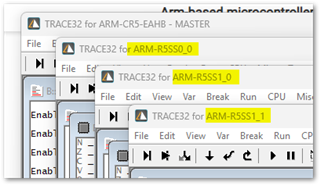

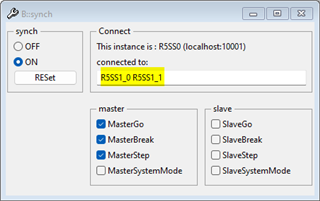

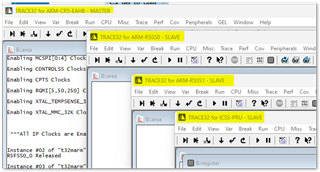

I ran '_am263px_allcoretype_connect.cmm' script expecting to see at four instances of TRACE32 for ARM-R5xxx. However, I only get the following:

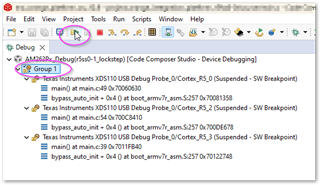

My project is R50_0, R51_0 and R51_1. (R50_1 is in lockstep mode).

I want to use Data,LOAD.Elf for R50_0, R51_0 and R51_1.

<Question>

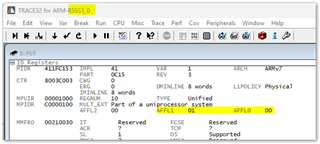

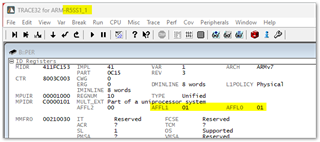

- It seems that 'ARM-R5SS0' = R50_0 and 'ARM-R5SS1' = R51_0, is that correct?

- If so, where is the instance for R51_1 in order to load its .out file please?

- If not, please correct my misunderstanding.

Thank you.