Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

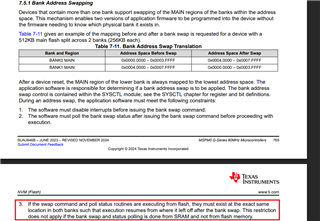

I'm implementing a firmware update using the CSC policy. In SysConfig, under the Configuration NVM (NONMAIN) section, I enabled "Enable CSC Policy" and "Enable Flash Bank Swap Policy." I then programmed the microcontroller, selecting the "Erase MAIN and NONMAIN memory" method.

The issue occurs when the CSC code attempts to swap the banks; specifically after calling DL_SYSCTL_issueINITDONE(), which follows DL_SYSCTL_executeFromUpperFlashBank().

if(bankswap == SWAP)

{

DL_SYSCTL_executeFromUpperFlashBank(); // Set swap bank0 to bank1

delay_cycles(160);

DL_SYSCTL_issueINITDONE(); // Issue INITDONE to trigger System Reset -> swap to bank1

}

else

{

DL_SYSCTL_issueINITDONE(); // Then issue INITDONE to trigger System Reset

}While debugging, I encounter the error:

Can't Single Step Target Program: (Error -2134 @ 0x0) Unable to control device execution state. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.1.0.3372)

Error: (Error -1001 @ 0x0) Requested operation is not supported on this device. (Emulation package 20.1.0.3372)

Trouble Halting Target CPU: (Error -2064 @ 0x0) Unable to read device status. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.1.0.3372)

Error: Connection to MSPM0 core failed. Possible root causes: 1) Debug access within NONMAIN was disabled or enabled with password. 2) Peripheral mis-configuration (e.g improper watchdog or clock). To see a more detailed diagnostic of the issue, please press the 'Read boot diagnostic' button.

The error also occurs when debugging is not active, as the microcontroller remains locked.

can someone help me? please

thank you